ժҪ��ӦIEEE1394ͬ����ͨ�����ߵĻ������������һ�ֻ��ڹ���ͨ����IEEE1394���źŴ���ϵͳ����ϵͳ�Ի����ֳ��ɱ��������(FPGA)��Ƶ�Э��ӳ��ģ��Ϊ���ģ�ʵ���˽�IEEE1394�ź�ͨ������ͨ�����д���Ĺ��ܡ���������������ϵͳ�ܴﵽ1.0625Gb/s�Ĺ������ʡ�

���յ���ϵͳ������ʮ��ķ�չ�����ھ�����ģ�⻯�����ֻ�ϵͳ��ת�䣬�����4�����յ���ϵͳ������Ҫ�ص�����ڵ�3�������ϣ��Ը��ٴ���������Ϣ����Ϊ���������ۺϻ���߶��ۺϻ���չ��ʵ����Դ�����������ںϣ������֡�ģ��������ҵ���ȣ�����������������ϵͳ�����ܣ���Щ���ܰ����������˽ṹ������������ɿ��Լ������ӳ����ܵȡ���ˣ�δ���Ƚ����յ���ϵͳ�и�վ��֮�������������Ϊ���ӣ�������Ƶ����Ƶ�ȴ��������ݣ��еĽڵ�����������1Gb/s�������еĵ����������ߺ���������˸��ٵ����ݴ���Ҫ��

�������ұ�ίԱ����1988�꿪ʼ�ƶ��Ĺ���ͨ��(Fiber Channel��FC)��һ�ָ��ٴ�������Э�飬�������иߴ������߿ɿ��ԡ�����ʱ���������Զ�����������ŵ㣬����֧�ֶ����ϲ㴫��Э�顣����ͨ������һ�ŵ�ʹ����ͬһ�����ӿ������ж����ϲ�ͨ����������Э���Ϊ���ܡ�Ŀǰ�Ѿ�ʵ�ֵ�ML-STD-1553������ͨ��Э���ӳ�䣬�Լ�ML-STD-1553Զ���ն����������ͨ������������ϵͳ�ۺϣ�Ϊδ�����յ���ϵͳ�в�ͬ���ߵĻ����ṩ��һ���µ�;����ʹ��ϵͳ�ڱ�����ͳ�������˺�Э���ͬʱ����ù���ͨ�����ṩ�ĸߴ�������

���ڴ����˼�룬���������һ��IEEE1394������ͨ������Э���ӳ�䷽�����ڴ˹��������ϣ������ֳ��ɱ��������(FPGA)�����������Э��ӳ�䷽��������Ӳ�������ʵ�֣������һ������FC��IEEE1394���źŴ���ϵͳ��

1 IEEE1394������ͨ����Э��ӳ��

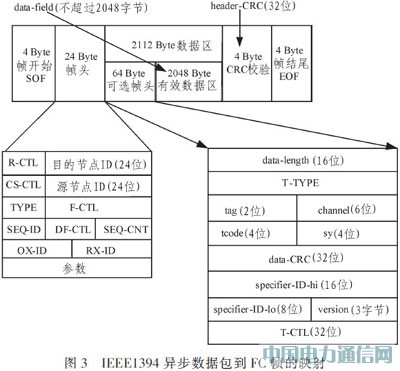

���ȼ�Ҫ���ܱ��������һ��IEEE1394������ͨ������Э���ӳ�䷽��������ϸ��˵���ɲο����ס�����Э��ӳ�䷽���Ļ���˼���ǣ���IEEE1394��FC���ݰ���ӳ������У�����FCԭ����֡��ʽ��ʽ����FC֡ͷ������Դ�ڵ��Ŀ�Ľڵ�ĵ�ַ�ֱ�ӳ��ΪIEEE1394Դ�ڵ��Ŀ�Ľڵ�ĵ�ַ������IEEE1394���ݰ��г������������������Ϣӳ�䵽FC��64Byte��ѡ֡ͷ�ϣ����������Ϣӳ�䵽FC����Ч�����������⣬����FCһ������֡����Ч����������ֻ��2048Byte������ͨ���������ʴ���200Mb/s��IEEE1394�ĵ�ʱ���ݰ��������ʴ���400Mb/sʱ���첽���ݰ��������Ч���Ƚ�����FC��Ч�������Ĵ�С����ˣ���IEEE1394���ݰ��ij��ȳ�����FC��Ч����������ʱ��Ӧ�ý������ݰ�ӳ���һ��������FC����֡���С�������IEEE1394�첽���ݰ���FC����֡��ӳ��Ϊ����˵������Э���ӳ����̡�

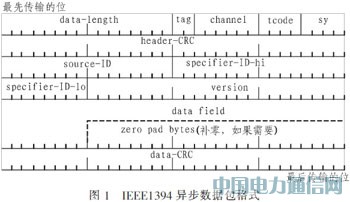

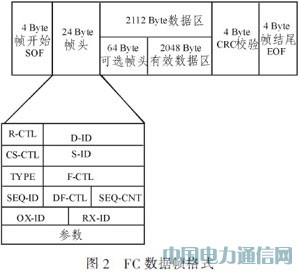

IEEE1394�첽���ݰ���FC����֡��ʽ��ͼ1��ͼ2��ʾ��ͼ3ΪIEEE1394����֡������ͨ��֡��ʽӳ���ϵ��

��ӳ����̵�˵����

1)Ŀ�Ľڵ��Դ�ڵ��ַ��IEEE1394��16λ���䵽24λ��ʹ�����ģ��ñȵ�һ��IEEE1394����Ҫ��

2)T-TYPE����ָ��������Ϣ�Ĵ������ԣ����������Ĵ��䷽����ն�-�ն�(NT-NT)���������ܶ��塣��NT-NT���ͽ����У���Ϊ����NT�ṩ����NT�ĵ�ַ������Ϊ����NT�ṩ����NT�ĵ�ַ��

3)T—CTL����ʵ��FC�����IEEE1394����֮�����Ϣ���䣬ʵ������֮�����·���ӣ����FC�����ն˻������������IEEE1394�ڵ�֮�����Ϣ���䡣

4)��IEEE1394�е�֡ͷCRCУ�������CRCУ��ֿ�����IEEE1394���ݴ����У����Ƚ��е���֡ͷCRCУ�飬������ִ���������������֡�������������뽫IEEE1394����CRC���ڹ���ͨ������֡�Ŀ�ѡ֡ͷ����֡ͷCRC���ڹ���ͨ������֡CRCУ���У����������ȼ��֡ͷCRC����ʡϵͳ������

2 IEEE1394���źŴ���ϵͳ�����ʵ��

2.1 ϵͳ�Ĺ���

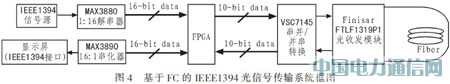

Ϊ�ڹ���ͨ������IEEE1394�źţ�����������������Ӳ��ƽ̨������ƵĴ���ϵͳ����Ҫʵ����������֡��ʽ��ת������Ҫʵ��FC-0��FC-1��FC-2Э����еIJ��ֹ��ܡ���������ƵĻ���FC��IEEE1394���źŴ���ϵͳ�ṹ��ͼ4��ʾ������IEEE1394�ź�Դ������FPGA��1394-FCЭ��ת��������Ҫ����Χ�ӿ������Լ������շ�ģ�飬ϵͳ��������1.0625Gb/s�����У�����ͨ��FC-0��Ĺ����ɹ��ת��ģ��ʹ����벢��ת��оƬʵ�֣���IEEE1394��FC����֡ӳ�估FC-1��FC-2�㹦����Ҫ����FPGA����Ӳ�������ʵ�֡�

2.2 ����FPGA�Ĺ���ģ�������ʵ��

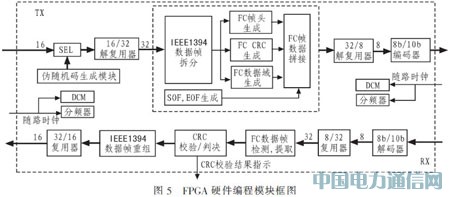

������Ƶ�ϵͳ�У�FPGA��Ҫʵ��IEEE1394��FC������֡ӳ���Լ�FC-1��FC-2�㹦�ܡ�����FPGA�Ĺ���ģ��ṹ��ͼ5��ʾ��

1)FC-1�㹦�ܵ�Ԫ����8b/10b����/����ģ���D/K����ָʾģ�顣

2)FC-2�㹦�ܵ�Ԫ�������ݽ���ģ�飬����ģ�鼰ϵͳ����ģ�顣

3)IEEE1394��FC������֡ӳ��ģ��(Э��ת��)��FPGA��Ƶĺ��IJ��֡��ò����ܹ���ɶ��ź�Դ������IEEE1394����֡��FCЭ�������֡��ӳ�乤��������IEEE1394����֡ת��ΪFC֡��ʽ��ͬʱ�ܴӽ��յ���FC����֡��ԭ��IEEE1394����֡��

4)FPGAƬ�ڵķ���(TX)���ֺͽ���(RX)���־�����������ʱ�ӹ���(DCM)�ͷ�Ƶ��ģ�飬DCM����ʹʱ���ź�ͨ��ʱ�����ﵽ����Ƭ�ڼĴ������Լ�СƬ��ʱ���źŵĶ�������ʱ�����ϵͳ�������ʡ�

���⣬Ϊ�˷�����û�����IEEE1394�ź�Դ������¶�FPGA�ڲ��Ĺ���ģ����е��ԣ���FPGA��TXǰͨ���������Է�����λ�Ĵ���IP�˹�����һ��α������з���������������ģ��IEEE1394����Դ����ͨ��1����ѡһѡ����ʵ���ⲿ�����ź����ڲ�α������е�ѡ���ܡ�

FPGA�ڲ��Ĺ�������˵�����£�IEEE1394���ݴ�16:32�⸴�������֮����IEEE1394���ݲ��ģ�飬������Ӧ��FC����֡��SOF��DATA��CRC��EOF�����ݶΣ����ɷ���FC֡��ʽ�����ݡ�����֮��32:8����ģ�齫32bit������������ݸ��ó�8bit������������ݡ�������8b/10b����ģ�飬���8b/10b�ı��빤������10bitλ����106.25MHz����������VSC7145����/����оƬ�������1.0625Gbs�����������SFP���շ�ģ�飬�ɹ��շ�ģ�齫�����ŵ��Ƴɹ��ź������

��RX���ղ��֣��ɹ��շ�ģ�黹ԭ�ɵ�������ͨ��VSC7145����/����оƬ����10bit�IJ���������ʽ���뵽FPGA�У���8b/10b���������룬���8bit��������(�ڽ�������У�����������ͨ���ж������ļ������б��Ƿ��ڴ�������г�������)��8b/10b��������������ͨ��1��8:32�⸴��ģ��⸴�ó�32bit�IJ������ݣ�����֧·����Ϊ26.5625MHz�����32λ��������ͨ��FC֡�����ȡģ�飬���ɱ�ʶ�ź���·�������CRCУ��/�о�ģ���У�����ͨ��CRCλ���㷴ӳ�Ƿ�������룬������ָʾ������֮��FC����֡����ΪIEEE1394����֡�������32:16����ģ�齫32bit����IEEE1394֡�������¸��ó�16bit�������ݣ���53.12MHz����·�ź�һͬ�ͳ�FPGAоƬ��

3 FPGA������֤

���������Xilinx Spartan3ϵ�е�Xc3s200��ʵ�֣�����Xilinx ISE 7.1���滷���½����˹��ܺ�ʱ�������֤������α������з��������ɵ�α�������ģ��IEEE1394����Դ���趨ÿ1000ByteΪһ�����ݰ�������

3.1 ���ܷ�����

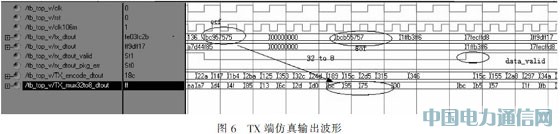

1)�ڷ��Ͷˣ�IEEE1394���ݰ�����⣬�����FC����֡������8b/10b������������������ͼ6�з��沨��tx_dtout����TX_encode_ dtout��ʾ��

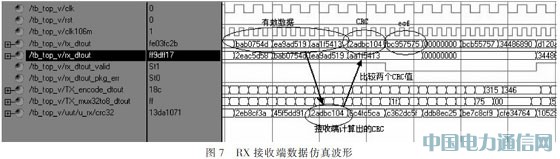

2)�ڽ��նˣ�FC֡�ṹ����ȷ��Ⲣ��ȡ����CRCУ����ȷ�������IEEE1394����֡��ʽ�������ͼ7�з��沨��tx_dtout��crc32��rx_dtout��ʾ��

��������ԣ�FPGAʵ��IEEE1394��FC����֡��ʽ��ӳ�书�ܣ���ģ�����������������ͨ�����ã���������

3.2 ʱ�������

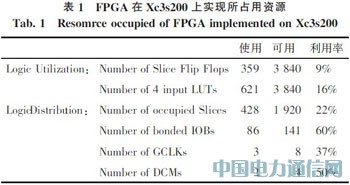

�������Xc3s200��ʵ�ֺ�FPGA��ʹ�õ���Դ���1��ʾ������ϵͳ��Դռ���ʽϵͣ�������������ܴﵽ135.245MHz������106.25MHz��Ƭ�������������Ҫ����ƴﵽ��Ԥ�ڽ����

4 ������

����ͨ������֧�ֶ����ϲ㴫��Э����ŵ㣬���������й����Ļ����ϣ�����FPAG�����������IEEE1394������ͨ����Э��ӳ�䷽��������Ӳ����ƣ�ͨ��FPGA���ܷ��漰ʱ�������֤�����᷽���Ŀ����ԡ����ô�FPGAЭ��ת��ģ�飬���Ļ�����˻���FC��IEEE1394���źŴ���ϵͳ�������˾����Ӳ����Ʒ�����Ŀǰ����ϵͳ����Ҫ���Թ�������ɣ������Ĺ�����ͨ��ϵͳ����ʵ�飬��ϵͳ���ܽ��з����о���