ժҪ����Էֱ���Ϊ1024×768��LCoS����д��Verilog HDL�������룬��quartus��9.1ƽ̨���ۺϱ��룬����Altera��FPGAоƬEP3C5E14 4C8�Ͻ����˹�����֤��ʵ������źŲ����������첽FIFO�ṹ����˿��첽ʱ��������ݴ������⡣Ƕ��FFT IP�˺ɽ�һ����ͼ����л���FFT�ı任����������ͼ���Ƶ�ס�Ϊ����ȫϢ3Dͼ��������ʾ�ṩ��Ӳ��ƽ̨��

0 ����

���ڿռ��������ļ���ȫϢ��ά��ʾ������Ŀǰ��������ʽLCD�ͷ���ʽLCoS��Ϊ�ռ����������Ըı�⾭���ռ�������(SLM)��Ŀռ���λ������ֲ����ﵽ�Թ���Ϣ�ĵ��ơ���ͳ�Ļ�����ʽLCD�ռ��������ļ���ȫϢ��ά��ʾϵͳ��������·���ӣ����ұ�������������������ݷ������ɼ��Լ����������������ϵͳӦ�õ�����ԣ��������ƹ㡣

�������ʽLCD��LCoS���й������ʸߡ����С�������ʸߡ������ߴ�С���ص㣬���Ժ�����ʵ�ָ߷ֱ��ʺ���ʾͶӰ�����ò�ɫLCoS����ʾ����RGB�IJ�ɫͼ������ѧ����ϵͳͶӰ���������ϣ�ʵ�ּ���ȫϢͼ�����ά��ʾ��

����FPGA����ʾϵͳ���������ƣ���һ��LCoS�ߴ�С������ʵ��ͶӰ�����ÿ�����̵�FPGA������Ϊ�����������������Ϳ��Խ�����������ͨͶӰ��һ������ͶӰ�豸��ʹ����ȫϢ��ά��ʾ�����˼�������ӹ�·�������������˸��ߵ�����ԣ�Ϊ���߳�ʵ�����ṩ���������ڶ�����Ϊ�ڴ�ͳ�ռ��������ϵõ���ͼ���ﺬ���ﲨ�Ͳο���ĸ��������γ�����������FPGA�Ͽ���ʵ��ͼ���˲�ȥ�룬ʹ�õ���ͼ���������������FPGA�ǻ��ڿɱ������Ԫ���������������ۺϡ����ֲ��ߡ�ʱ��Լ���Ĵ�����¼��FPGA������FPGA�ͽ��㷨����Ӳ�����ˣ�������Ϊר��оƬ���������ڲ��ź���ʱ��ȫ��Ӳ����������ʱ���ڴ������ݰ��ƺ��ӵ���ѧ�����Լ�һЩѭ������ʱ������ͼ���FFT�任��FPGAӲ������Ҫ�����������ö࣬������FPGA����ʵ�ֶ������㷨��Ӳ�����١�

��������ԭ��������˻���FPGA��LCoS�������뼰ͼ���FFT�任ϵͳ��Ϊ����ȫϢ��ά��ʾͼ��������ʾ�ṩ��Ӳ��ƽ̨��

1 ϵͳ���

1.1 ϵͳģ���ͼ��

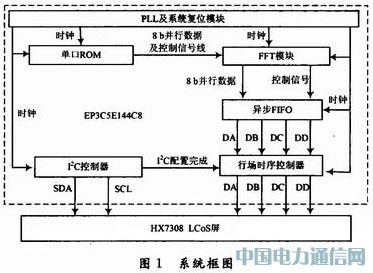

��ϵͳ����cyclone��EP3C5E144C8����оƬ��5136��LE��95���û�I/O��2��PLL���Լ�46��Ƕ��ʽ�˷�����423936b���ڲ����Ĵ����������ḻ����Դ����ȫ������ΪLCoS������������������ʾ������Himax�ķ���ʽLCoS��HX7308����ֱ���Ϊ1024×768������֧��256���Ҷ���ʾ���������õ��г�������·�����ⲿ����ʱ�ӵ������غ��½��طֱ����8b×4dotsͼ�����ݣ��Ᵽ֤�˳�Ƶ�ɸߴ�360Hz��

ϵͳ�������ͼ��ͼ1��ʾ��

1.2 PLL��ϵͳ��λģ��

����Altera�����IP�ˣ��ⲿ����ʱ��Ϊ20MHz������Ƶ��õ�������ģ�������ʱ�ӣ��Լ�LCoS������ʱ���źš�Ϊ��ֹϵͳ�첽��λʱ�Ĵ�����������̬�������PLL��ǰ���ͺ�D����������Ϊ�����locked����������ȶ������Ż�����Ϊ�ߵ�ƽ������Ϊ��֤����ģ��õ��ȶ���ʱ���źţ���locked���ź��ⲿ���븴λ�ź�rst_n�������Ϊ����ϵͳ�ĸ�λ�źš�

1.3 ����ROMģ��

����FPGA�ڲ���M9K�洢����Դʵ�ֵĵ���ROM��ΪԴͼ������ݴ洢�������ֱ���Ϊ176×144(QCIF)��256�Ҷ�λͼͼ���ʼ��������ROM������������Ϊ25344B�����첽FIFOûд��ʱ������ROM����ͼ��洢��ַ�������ͼ�����ݸ�FFT�������ٸ���Ҷ�任������������ͼ�������ݴ浽FIFO)��ȴ��г�ʱ�������ģ��ȡ�á�

1.4 �첽FIFOģ��

�������ݵ�ַ���2λ��Ϊ4�����䣬��/дָ��ֱ��ijһ�������������/дָ�����ʱͨ������������FIFO�Ѷ��ջ�����д����־�źš�Ϊ�����ַ�źű仯ʱ����ð�վ�������д��ַ�Ͷ���ַָ�붼���ø�������롣�ڶ��ձȽ���ģ���д���Ƚ���ģ���������FI-FO“����”��“����”������ƣ���Ч�ر�֤��FIFO��ȷ����Ĺ�������дʱ��wrclk�������أ��첽FIFOÿ����ַ��Ӧ�Ĵ洢��Ԫ�ﱻд��8bits���ݣ��ڶ�ʱ��rdclk�������أ�FIFO�Ŀ�������ַ�ϵ�32bits�������������FIFO�������൱��дFIFO���ʵ�4���١�

1.5 I2C״̬��ģ��

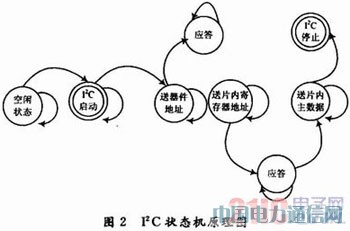

û������I2C��������ʱ��״̬�����ڿ���״̬��������I2C��������ʱ��״̬����״̬��־λ�Ŀ���������������õ�ַ���������ݡ����������ý���ʱ��״̬������ֹͣ�źţ��������������iic_config��֪ͨ�г�ʱ�������ģ�鿪ʼ������������֤��LCoS��������ȷ�����¹�����״̬������ԭ����ͼ2��ʾ��

1.6 �г�ʱ�������ģ��

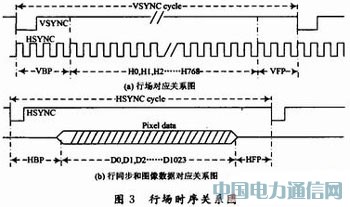

����ˮƽ������hcnt�ʹ�ֱ������vcnt��������ʾ��ÿ��ʱ����������8������ֵ��������ʾ1024������ֵ����������Ϊ128��Tclk(��ʱ������)����hcnt������ֵΪHBPʱ��ʾ����Ч��ʾ����ʼ��hcnt������ֵΪHBP+128ʱ��ʾ����Ч��ʾ���������hent������ֵΪHSYN-Ccycleʱ�����һ����ʾ��vcnt��������1����vcnt������ֵΪVBPʱ����ֱ��Ч��ʾ����ʼ����vcnt������ֵΪVBP+768ʱ����ֱ��Ч��ʾ�����������vcnt������ֵΪVSYNC cycleʱ�����һ֡ͼ����ʾ���г�ʱ���ϵ��ͼ3��ʾ��

1.7 FFTģ��

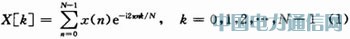

FFTV 9.1 IP�˲���Cooley-Tukey��-2 DIF�㷨����FFT�任ԭʼ��ʽΪ��

��Ϊ������������ģʽ�������任�����ݿ��������������������ݲ�����Ϊͼ�����ݵ������ֹͣ���������ͬʱ��������Ҳ������Ϊ��������������������ֹͣ�������룬��֤������ת���ʹ���������ԣ���������ݴ������ٶȺ�Ч�ʡ���ΪFFTͨ���첽FIFO����Ļ������ݣ���FIFO�Ķ�������д���ݵ�4���٣������ʱ�Ӻ�дʱ�Ӷ�Ϊ100MHz����ô�п��ܻ���ijһ�������FIFO��ȡ�գ���������Ļ�����Ч���ݵ������Ϊ��֤FIFO����Ļ���ͼ�����ݵ������ԣ���Ҫ�������VBP��VFP��HBP��HFP��ʱ�䣬��ÿһ�еĿ�ʼ�����FIFOû������ô����FFT��������ת������ͼ��ķֱ���ΪM×N������VBP�ڼ�FIFO�ѱ�д������FIFO��FFT�ˡ��г������Լ�ͼ��ֱ��ʼ��ϵ�ļ��㹫ʽ���£�

ʽ�У�Deepth���첽FIFO��������ȣ���λΪB��THSYNC cycle�������ڣ�Tclk���첽FIFO��FFT�ˡ��г�ʱ�������ģ�������ʱ�����ڡ�����>Oʱ��ϵͳ������ʵʱ�ش���ͼ����<Oʱ���ᵼ������ĻijЩ�е���Ч��ʾ����û����Чͼ�����ݿɹ���ʾ���������ƻ���ͼ����ʾ�������ԡ��ɸ������Ϲ�ʽ�������FIFO����Լ�ѡȡ���ʷֱ��ʵ�ͼ������У��첽��FIFO��FFT�ˡ��г�ʱ�������ģ�������ʱ��Ϊ100MHz��FIFO���Ϊ256B��������Ϊ336��Tclk��MΪ174��NΪ144���������>0��

2 ʵ��������Ͳ����������

ͼ4�Dz���Modelsim 6.5b���й��ܷ���Ľ��������Quartus��V9.1�Դ���TimeQuest Timing Analyzer����ʱ��Լ������ʵ����ϵij��źŲ��������ͼ5��ʾ����ɨ��Ƶ���Ѵﵽ368Hz��������������������ź�Ҳ������ʱ��Ҫ������FPGA������Դ���ƣ���ͼ������256��FFT�任����ʵ����֤��������ܹ�ʵ��ͼ���ʵʱ����������ﵽ��Ԥ�����Ч����

3 ����

����Himax��LCoS��HX7308BTJFA��Ϊ��ʾ��������ߴ�Ϊ14.43mm×10.69mm����С�ɸ�1ö1ԪӲ������⣬������ʵ����άͶӰ��ʾ����VerilogHDL�к�ǿ�Ŀ���ֲ�ԣ������Ժ�Դ����������ά����FPGA�ڲ���Դ�Ͼ����ޣ�����������֪������ʾ�ֱ��ʽϴ��ͼ�⿿�ڲ���Դʵ���첽FIFO�Dz����ܵģ������ڴ�������ַ�������һ����һƬ���ܽϸߵ�оƬ������дFIFO���ʵ��ڶ�FIFO���ʵ�Ҫ���������ܴﵽ��/д���ݵĶ�̬ƽ�⣬��֤��ͼ���������ʾ���ڶ��������ⲿ�洢��SDRAM�洢Դͼ���FFT����������ݣ�����DDRII������ȡ���ݣ�ʹ��/дFIFO������ƥ�䡣��FPGAоƬ��Դ���ƣ�����Ʋ��÷ֱ���Ϊ176×144��ͼ�������ϵͳ������֤����δʵ��ͼ���˲��Լ�FFT��任��δ���ɽ�������ֲ�ڸ߶˵�FPGAоƬ�ϼ����������ݴ������ܡ�