ժҪ���ڷ���Sony��˾ICX098BQ����CCDͼ��������ʱ��Ļ����ϣ��Կɵ����ع�ʱ���CCDʱ����������Ӳ����·������ơ�ѡ��FPGA������ΪӲ�����ƽ̨��ʹ��VHDL���Զ�ʱ���ϵ������Ӳ������������QuartusII 8.0������Ƶ�ʱ�����������˹��ܷ��棬����Altera��˾�Ŀɱ��������Ϊ���Ľ���Ӳ�����䡣ʵ�ʲ��Ա���������Ƶ�����ʱ�������ܹ���������CCD������Ҫ��ʵ�������Ŀ�ġ�

CCD�����ù��ת��ԭ����ͼ���ź�ת��Ϊ�����ţ�����һ�����ռ���ֲ��Ĺ�ѧͼ��ת����Ϊһ����ʱ����ֲ�����Ƶ�źŵİ뵼��Ԫ����������������С�������ᡢ���ĵ͡������ȸߡ������ȶ�������������ɨ��ͱ���ͬ������ӿڵ��ŵ㣬���㷺Ӧ����ͼ�кͷǽӴ�ʽ������CCDӦ�õĹؼ�����֮һ��������ʱ��������ơ���ֱ�ӹ�ϵ��CCD���źŴ���������ת��Ч�ʺ�����ȵȹ��ת�����������Sony��˾����CCD ICX098BQ�Ĺ���ԭ��������ʱ���Ҫ����������ʱ�������ľ�����ƣ�ʹ��VHDL���Զ�����ʱ��������ʵ�ַ���������Ӳ������������Quartus II 8.0������Ƶ�ʱ�����������˹��ܷ��棬�ڸ�����ʱ�����������£���Sony��˾ICX98BQ����CCD����������źŲ��ν�������֤��

1 CCD����ϵͳ

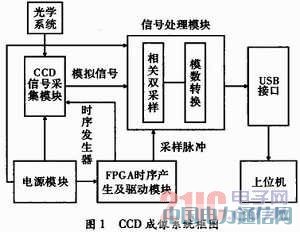

CCD����ϵͳ��ͼ1��ʾ��Ŀ��ͨ����ѧϵͳ������CCD�ϡ���ƫ�õ�ѹ����������������£�CCD��ɹ��ɵ�ת�ơ������ȹ����������ź�ת���ɾ���ֱ��������ģ����źš��γɵ�ģ�������ž����źŴ����������г��롢�����ģ��ת�������ݴ��䵽��ʾ���������ϣ����к��ڴ�����������ϵͳ�У�CCD�źŲɼ�ģ���ǹؼ����Դˣ���Ҫ��CCD�źŲɼ����з�����

2 ����CCDͼ��������ʱ�����

2.1 Sony ICX098BQ������CCD

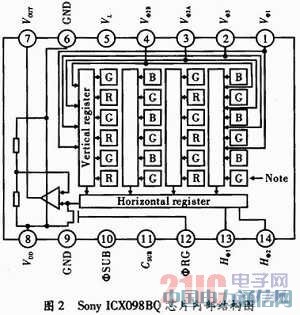

ICX098BQ��Sony��˾������һ��1/4Ӣ��(0.635cm)�����пɱ���ӿ��ŵ��м�ת���Ͳ�ɫ����CCDоƬ��оƬ�ṹ��ͼ2��ʾ����оƬ�����ȸߣ�������С�����нϺõĿ���ɢ���ܡ�

ICX098BQоƬ�ɸй����С���ֱ��λ�Ĵ�����ˮƽ��λ�Ĵ���������Ŵ���4����Ҫ������ɡ�Ҫʹ��CCDоƬ������������Ҫ8·����ʱ�����������ֱ�Ϊ4·��ֱת��ʱ��Vφ1��Vφ2A��Vφ2B��Vφ3�����ƴ�ֱ��λ�Ĵ����еĵ���ź���ˮƽ��λ�Ĵ����ƶ������е�Vφ2A��Vφ2BΪ+15V�ߵ�ƽʱ��Ϊ����ת��ʱ�ӣ����й����е��źŵ��ת�Ƶ���ֱ��λ�Ĵ����У���·ˮƽת��ʱ��Hφ1��Hφ2������ˮƽ��λ�Ĵ����еĵ���ź���ǰǨ�ƣ���λ��ʱ��RG��ʹˮƽ��λ�Ĵ����еĵ���ź�˳���������Ƶ��Ϊ10MHz��ֱ�Ӿ���CCD����źŵ�ˮƽ���Ƶ�ʲ������ع����ĵ��ӿ���ʱ��φSUB��

���������źž���CCD����ʱ��������������������CCD�������ź������࣬��λҪ���ϸ�����Ҫ���ֵ�ѹ����������˽���ʱ���������Ƴ��߾��ȵ�����ʱ���·������Ĺؼ���

2.2 ����ʱ�����

ICX098BQоƬ��һ���������ڷ�Ϊ4���Σ��й�Ρ���ֱת�ƽΡ�֡ת�ƽκ�ˮƽ�����Ρ��й�ν��й��ת������ɸй����еĵ�ɻ��ۡ���ֱת�ƽ�ʵ�ָй����л��۵ĵ�ɰ�����ת�Ƶ����ڵĴ�ֱ��λ�Ĵ�����֡ת�ƺ�ˮƽ�����ΰ�����ɰ��Ӵ�ֱ��λ�Ĵ�����ˮƽ��λ�Ĵ�������ת���Լ���ˮƽ��λ�Ĵ���������Ŵ����Ĵ��������

��CCD���������У�������Vφ1��Vφ2A��Vφ2B��Vφ3�Ŀ����£��й����еĴ�ֱ��λ�Ĵ�������һ�ε��ת�ƣ���֮ǰ���������ĵ�ɳ��������Ϊ��һ����������Ȼ��ֱ����ʱ��V1������һ�θߵ�ƽ���˿̣�����ʱ��V2A��V2B����Ϊ+15V�ĸߵ�ƽխ���壬����ʱ��Ѹ�ٽ��й������е��������ص�ɲ��е�ת�Ƶ����ڵĴ�ֱ��λ�Ĵ����С���ÿ���������ڼ䣬��ֱ��λ�Ĵ����еĵ�������ഹֱ����ʱ��Vφ1��Vφ2A��Vφ2B��Vφ3�������������е���ˮƽ�Ĵ���ת�ơ���ʱˮƽ����ʱ��Hφ��Hφ2���ֲ��䡣���������ڼ䣬ת�Ƶ�ˮƽ�Ĵ�����һ���źŵ����Ƶ��Ϊ10MHz������ˮƽ����ʱ��Hφ1��Hφ2���ƣ�������ɢ�Ŵ���ˮƽת�ơ�����Ŵ����Ը�λ��ʱ��RG��Ƶ�ʽ����ص����һת�����źŵ�ѹ���������������˵õ����ѧͼ���Ӧ��һ�е���Ƶ�źš�

3 ����VHDL��ʱ���������

��������CCD����ʱ��ĸ����ԣ�ѡ��Ӳ����������VHDL���CCDʱ��VHDL�����Զ����µ���Ʒ�ʽ�����н�ǿ��Ӳ�����������ͷ����������ڳ����У��������������˰�����������˺�10������ˡ�

��������ʱ��������ʵ�ֳ���Ϊ����Ƕ��ѭ�����������̲���3��ʽ״̬������ɡ�һ��CCD���������������£�

(1)��ˮƽ�Ĵ���������ո�λ��

(2)��ֱת�ƣ�����ɴӸй���ת�Ƶ����ڵĴ�ֱ��λ�Ĵ�����

(3)����֡ת�ƺ�ˮƽ�����Ρ�֡ת��һ�У�ˮƽ����һ�У�ֱ����֡������ϡ�

(4)���أ���ȡ��һ֡�������ز���(1)��

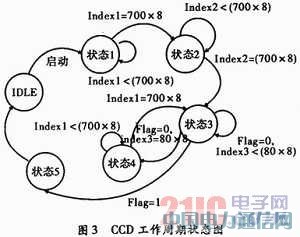

״̬ת��ͼ��ͼ3��ʾ��

IDLE��Ϊ����״̬��������������ת��״̬1��

״̬1��ΪԤ����״̬������ˮƽ�Ĵ����ڵĵ�ɣ���ˮƽ����700����ɺ�ת��״̬2��������ѭ����

״̬2��Ϊ��ֱת��״̬��ʹ�й����ĵ��ת�Ƶ���ֱ��λ�Ĵ�������ֱת�ƺ�ת��״̬3��

״̬3��֡ת��״̬������FlagΪ����Ч��־����Flag=1ʱ���������״̬����ʼ��һ֡�Ĺ�����

״̬4��ˮƽ����״̬��

״̬5������״̬��ת�����״̬����ʼ��һ֡�Ĺ�����

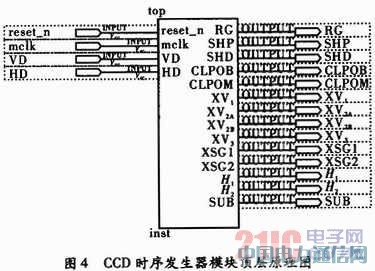

���ݷ�������Ƴ���������ʱ��Ķ���ԭ��ͼ����ͼ4��ʾ��

��CCDʱ������ģ���У�����Ϊʱ�Ӻ�λ�źţ��Լ���·ͬ���ź�VD��HD���������CCD���������10·�ź��⣬������SHP��SHD��·�������˫�����ĵ�·�Լ�����Ԫ������Ԫ����ʱ��

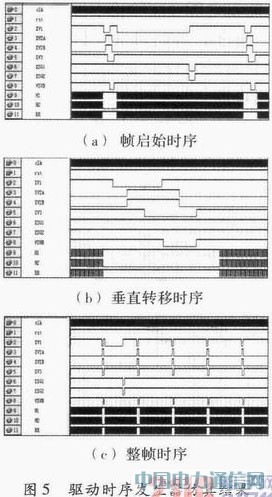

�ڶ�VHDL����������ʱ���������б��������ʱ���������й��ܷ��棬��������ͼ5��ʾ��

ͨ����FPGAоƬ��������ء�������ģ�鼯����CycloneIIϵ��оƬEP2C8T144C8N�С���ʱ����������ģ�������Դռ���ʽ�Ϊ3����

4 Ӳ��ʵ���Լ����Խ��

CCD�źŲɼ�������·Ӳ��������Ҫ��Ϊ�������֣���CCD������·��ƫ�õ�ѹ����ơ�

4.1 ƫ�õ�ѹ��·

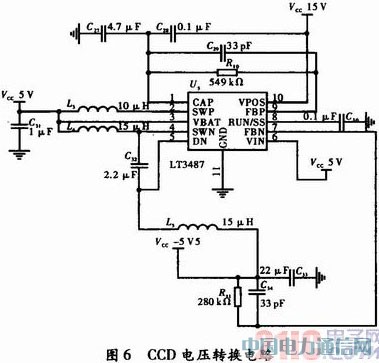

��ICX098BQ�������ֲ���з�����Hφ1��Hφ2ˮƽ��λ����������ѹ���ֵΪ3.3V���ֱ�Ϊ-3.3��0V��0��3.3V��Vφ1��Vφ3��ֱת�ƹ�����ѹΪ5.5 V(-5.5��0 V)��Vφ2A��Vφ2BΪ����ƽ��������ѹΪ(-5.5V��0V��+15V)�������Ҫ-5.5V��+15V��ΪCCD��ֱ����ʱ��Ĺ�����ѹ��ƫ�õ�ѹ+15V��-5.5V����Linear��˾������LDOLT3487��ã�ƫ�õ�ѹ������·��ͼ6��ʾ��

LT3487��һ�оƬ��ѹ���������ڵ������ѹ(2.3��16 V)�����ϣ����������ѹ��������ͬ������ѹ����ȣ�������Ͽ����ܿɱ����������ر��ڼ����ֱ��©�������µĹ�����ġ����������ѹֵΪ+5V��ͨ��USB�ӿڴӵ��Եõ����乩��������ȫ�ܹ�����������CCD��·�ĵ������ġ�

4.2 ��������·

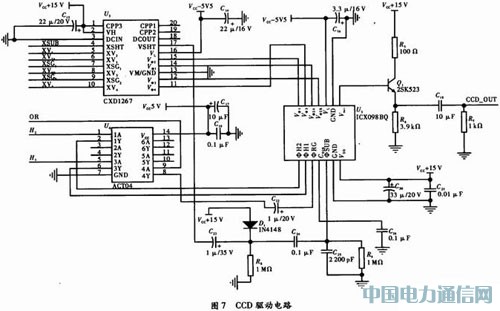

��ͼ7��ʾ��CCD�������������ʱ�����CycloneIIϵ������EP2C8T144C8N��������CCD���������4·��ֱ����ʱ��Vφ1��Vφ3��Vφ2A��Vφ2B�У�Vφ1��Vφ3Ϊ����ƽ��Vφ2A��Vφ2BΪ����ƽ����FPGA�������ź�ֻ��‘0’��‘1’����״̬���Դˣ��ɽ�ʱ�������е�XV2��XV3ʱ��ֱ���XSG1��XSG2ʱ����������ϳ�������CXD1267AN���кϳ�������Vφ2A��Vφ2B��

��ͼ7��ʾ����FPGA������ʱ��������10·�ź��У�XV1��XV2��XSG1��XV3��XSG2��XV4��������ϳ�������CXD1267AN�ϳ�ΪVφ1��Vφ2A��Vφ2B��Vφ3����H1��H2��λ����RRͨ��ACT04�����������CCD���й�����������H1��H2��RG��������ѹ��������CCD��ˮƽ����������������·��-5.5V��+15V�ĵ�ѹ�¹������ڵ�ѹƫ�õ�·��������·�Ĺ����£�������CCD�ź�Ϊ����ֱ��������СΪ����mV�Ľ����źš�

4.3 Ӳ�����Խ��

�����ͼ����ѧ��ͷͶ�䵽����CCD�ϣ���������ʵ�ֵ�����ʱ����������CCD������������ʾ�����Ը�ֱ���CCD�źŽ��в�����

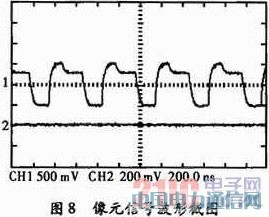

ͼ8ΪCCD�����ijһ���и��й���Ԫ����źŵIJ��Σ�ÿ�����ڴ���һ����Ԫ��ÿ�����ص�Ԫ��Ϊ3���֣����Ƿֱ��Ǹ�λ�������롢�ο���ƽ�����ݵ�ƽ��ÿ�������еļ��Ϊ��λ�������뵽CCD�Ķ������ݣ���CCD����������γɣ�ÿ�����ظ��ܵ����źŵ���Чֵ�ɲο���ƽ�����ݵ�ƽ�IJ��ʾ���ɴ˿ɼ���������ʱ������������CCD������������

5 ������

ʱ����Ʒ�������VHDL���Խ�����ƣ���EDA����������Ƶ�������·�����˷��档��������������������·�ܹ���������CCD����ʱ�����