ժҪ��Ϊ�����̾���������������ڣ�ʹӲ����Ƹ�������ԣ��ڽ��ܾ���������ԭ���Ļ����ϣ�������һ�ֻ��ڿɱ��������������ģ�黯��Ʒ���������VHDLӲ����������ʵ��CDMA2000ϵͳǰ����·�����������ķ�������������Quartus�������µķ�����������FPGA��������֤ʵ�֡������ʵ�鶼֤�������ַ����Ŀ����Ժ���ȷ�ԡ�

0 ����

��ͨ��ϵͳ�У����������ź��ڴ���������ܵ����ָ��ŵ�Ӱ�죬ʹ�ź���Ԫ���α仵���ʴ��䵽���ն˺���ܷ��������о���Ϊ�����һ���⣬ͨ�����������ͨ��ϵͳʱ������Ӧ�Ӻ�����ѡ������ƶȡ���������Լ������ʵȷ��濼�ǣ�����ȡ���ϴ�ʩ��������Ҫ��Ҫ���Dz�����ƴ�ʩ����CDMA 2000ϵͳ��ǰ����·�ͷ�����·�оͲ����˾���������ʵ��ǰ��������(FEC)��

FPGA�ǿɱ����������������Ҫ�ŵ����ڿ��Խ���EDA����ͨ��������̶�������Ӳ���ṹ������ʽ�����ع������ʹ��Ӳ����ƾ���������Ƶ�����Ժͱ���ԡ�����Ʋ���VHDL���Բ�ѡ�ÿɱ����������Quartus������ʵ��CDMA 2000ϵͳ�е�ǰ����·������������

1 ����������ԭ��

����������P.Elias��1954������������ģ�����һ�ַǷ����룬ͨ������������ǰ���������Ϊ�����ܶ�������ʵ����������ڷ����룬�����豸���Դ�A.J.Viterbi��1967�귢����һ����Ч�������㷨������J.Omura��1969��֤������һ��ML�����㷨��ʹ��Vit-erbi�����㷨�ľ�����ͳ�Ϊ�ִ�ͨ��ϵͳ�бز����ٵı��뷽����CDMA 2000ϵͳ����ô��ֱ��뷽����

1.1 ����������ԭ��

��������������ͬ����������������м���ģ��������������κ�һ��ʱ���ڲ�����n����Ԫ������ȡ�������ʱ���е�k����Ϣλ�����һ�ȡ����ǰN-1�ι涨ʱ���ڵ���Ϣλ����������������n����Ԫ�����������ÿһ��kλ����Ϣ�����йء�Ϊ�˱���˵�����⣬������涨��������r=k/n�����У�k��ʾһ���������������Ϣλ����n��ʾ��Ӧ������kλ��Ϣ��������������������⣬��K��ʾԼ�����ȣ������ڱ���������λ�Ĵ����ļ�����ʵ���ϣ���һ����λ�Ĵ����Ƕ���ġ�

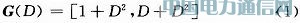

��������������̵ķ����ܶ࣬�磺����ʽ����������״ͼ������ͼ�ȡ��������������������ṹ������صĶ���ʽ����˵��������ı���ԭ������֪һ��������r=1/2��Լ������K=3�ľ����������������������ɶ���ʽ����Ϊ��

ʽ�У�DΪ�ӳ����ӣ����ɶ���ʽ�ĵ�һ��Ϊ1+D2����ʾ����������ĵ�һ����Ԫc1����������Ԫb1��ǰ������Ԫb3��ģ2�ͣ���ڶ���ΪD+D2����ʾ����ĵڶ�����Ԫc2Ϊǰ����������Ԫb2��b3��ģ2�͡�

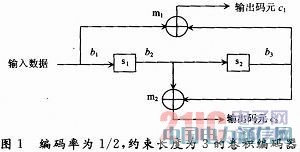

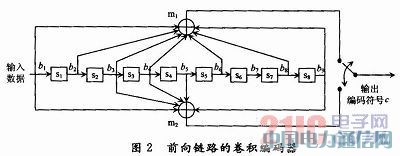

���ݾ���������ɶ���ʽ�����ֱ�ӵõ��������Ľṹͼ����ͼ1��ʾ��ͼ��s1��s2Ϊ��λ�Ĵ�����m1��m2Ϊģ2�ͼӷ���������b1������ǰ�������Ϣλ����λ�Ĵ���״̬b2��b3�洢��ǰ����Ϣλ��c1��c2���������������Ԫ��

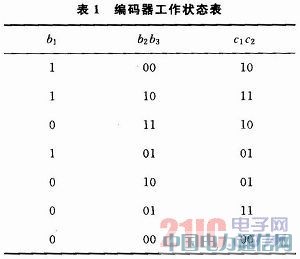

�ھ�����ı�������У���������ȫ��״̬������������ص�ȫ��״̬���ʵ�������Ϣ��Ҫ�������������K-1��ȫ����Ϣ������ʹ�������ص�ȫ��״̬����˱���������ʼ״̬Ϊ�㣬��b1b2b3Ϊ000�����������ϢλΪ11010ʱ��Ϊ��֤�����ȫ����Ϣλ����ͨ����λ�Ĵ�����������λ�Ĵ������и�λ����������Ϣλ���Լ�����ȼ�һ���㣬�������㣻��ʱ��Ӧ�������Ԫ����Ϊ��10111001011100����������λ�ɵñ������������Ϣ��1011100101���������������б�������״̬���1��ʾ��

1.2 CDMA 2000ϵͳ�е�ǰ����·����������

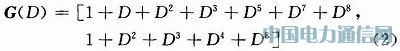

��CDMA 2000ϵͳ�У�ǰ����·ʹ�ñ�����Ϊ1/2��Լ������Ϊ9�ľ�����������ǰ����·����������ɶ���ʽ����Ϊ��

�ɴ����ɶ���ʽ����ɵ�ǰ��������Ľṹͼ����ͼ2��ʾ��ͼ��s1��s8Ϊ��λ�Ĵ�����m1��m2Ϊģ2�ͼӷ���������b1������ǰ�������Ϣλ����λ�Ĵ���״̬b2��b9�洢��ǰ����Ϣλ��c���������������Ԫ��

2 CDMA 2000ϵͳ��ǰ����·������������ʵ��

2.1 CDMA 2000ǰ����·�����������ĵ�·���

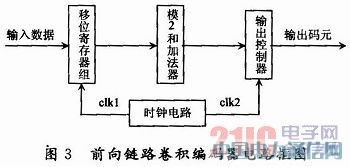

����Ʋ���ģ�黯����Ʒ���������CDMA2000ϵͳ�е�ǰ����·�����������Ĺ��ܽ����ڲ��ṹ��Ϊ����λ�Ĵ����顢ģ2�ͼӷ���������������Լ�ʱ�ӵ�·���ĸ�ģ�飬ÿһģ���Ӧһ����VHDL������ļ����������ڳ���ı�д�͵��ԣ��Ӷ���������������ĵ����Ѷȣ�����������Ŀ�ά���ԺͿɶ��ԡ�ǰ����·��������������ɿ�ͼ��ͼ3��ʾ��

���У�ʱ���ź�clk1��clk2���ɻ�վ������(BSC)��ʱ�ӵ�·ֱ���ṩ�����ɱ�����Ƶ�ʱ�ӵ�·����վ������(BSC)�ṩ��ԭʼʱ���źŽ��з�Ƶ�õ����������������������ݺϳɵ�·�����ε�·�����֡�

2.2 CDMA 2000ǰ����·�����������ķ���ʵ��

���ݾ�����������·��ͼ������VHDL���Ա�дǰ����·������������Դ�������뵽Quartus�������н��б��롢���桢�ۺϵõ��������ļ���Ȼ��ͨ����������������ơ�

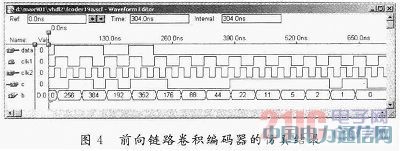

����ǰ����������ij�ʼ״̬Ϊ�㣬����b1��b9Ϊ00000000���������ϢΪ11010��Ϊ��֤�����ȫ����Ϣλ����ͨ����λ�Ĵ�����������λ�Ĵ������и�λ������Ϣλ���8���㣬��������Ϊ11010111000001111111101100,������ʱ����������data������Ϊ9.6Kb/s�������Ԫc������Ϊ19.2Kb/s����������ͼ4��ʾ������bΪ�Ĵ��������ʱ�̵�״̬��

��ǰ����·�������������������һЩ��Ҫע������⣺����Ҫ��ȷVHDL���Բ�ͬ�������ļ�������ԣ�����һ��Ӳ���������ԣ��������Ķ����ǿ۵ĵ�·ϵͳ����Σ���ͬ��EDA���߶�VHDL���Ե�֧�̶ֳȲ�ͬ����������в��õ�Quartus��������Ҫ����Կɱ����������������������֧�����е�VHDL��䣬��ֻ֧��RTL����������֧����Ϊ�����������У����������Ҫ�������Ҫ��Ϳɱ������������Դ������ٶȵȽ��к�����ѡ������в��õ�EP2C8Q208�����Ϳ�������Դ���ٶȷ����Ҫ��

3 ����

����ʵ����һ��������CDMA 2000ϵͳ��ǰ����·������������ͨ���������·����ơ�����͵��⣬����������������ɴﵽCDMA 2000ϵͳҪ����һ����ʵ�ü�ֵ��ͬʱ������Ʋ��û��ڿɱ������������VHDL���Լ�EDA���߽�����Ƶ�˼·�����������������ڣ������˳ɱ����������ƵĿɿ��ԡ�����ԣ�Ϊͨ��ϵͳ����ṩ��һ����Ч����Ʒ�����