引言

在录井仪器中,深度系统是最重要的部分,离开了深度系统中的井深,仪器中大部分参数都将失去意义[1]。而在深度系统中,大钩高度的测量是最为关键的。通过绞车信号的实时数据检测,可得到与大钩高度相关的绞车脉冲信号计数值,将该值传入上位机,通过相应的计算可以得到实时的井深。

同时,基于太阳能和蓄电池供电的无线录井数据采集与传输系统要求现场绞车信号检测电路必须具有低功耗、小尺寸和抗干扰性强的特点。因此,采用分离元器件所设计的传统的绞车信号测量电路就不能满足无线录井系统的这些特殊要求。

美国Xilinx公司的CoolRunner II系列CPLD芯片XC2C64A结合XC9500系列的高速度、方便易用和XPLA3系列的超低功耗等优点,具有低功耗、高密度、在系统可编程和抗干扰能力强等特点[2],在一颗芯片上就可以代替多颗传统逻辑芯片来实现复杂的组合与时序逻辑控制,能够达到低功耗、小尺寸和抗干扰性强的优良性能[3]。

无线录井绞车信号检测电路的设计与实现

绞车顺时针旋转时, 传感器输出A相波形超前B相波形90°;逆时针旋转时,输出A相波形滞后B相波形90°。其后的鉴相(方向鉴别)、倍频和计数就是基于如上输出的两相脉冲信号。

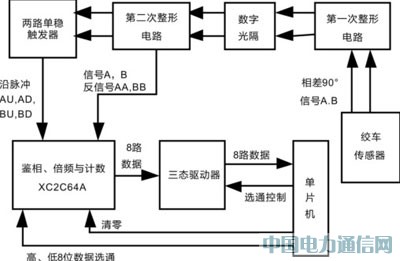

绞车信号检测电路的整体结构(图1),包括绞车信号的整形、隔离、鉴相、倍频、计数和数据读取接口等部分。

信号A和信号B是来自绞车传感器的相位差90?的两路脉冲信号,先经过第一次施密特整形,抑制现场干扰和线路衰减引起的脉冲波形畸变,转换为标准的脉冲信号;然后经数字隔离器进行电气隔离,隔离电路一方面对后面的电路起保护作用,另一方面起电压变换的作用,将信号转换为3.3V标准电压的脉冲信号;再经过第二次施密特整形电路进行整形,此次整形的主要目的是将两路脉冲信号的波形进行变换,产生A、B、AA(A的反相)和BB(B的反相)四路信号。

图1 绞车信号检测电路结构框图

经第二次整形后,A、B两路信号经过单稳态触发器,在其上升沿和下降沿处分别进行触发,得到四个窄脉冲信号AU、AD,BU、BD。

得到的A、B、AA、BB、AU、AD、BU、BD共8路信号输入到CPLD XC2C64A,进行倍频、鉴相和计数等处理,并在单片机的控制下对数据进行输出或清零。

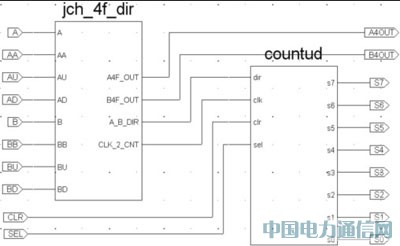

根据如上的设计原理,采用Xilinx公司的EDA软件ISE和模块化设计[4]的方法设计了无线录井绞车信号的检测电路,其顶层设计电路如图2所示,该电路包括两个子模块:倍频、鉴相子模块jch_4f_dir,具有4倍频和方向鉴别功能;16位二进制可控加减计数与数据接口子模块countud,具有加/减计数(由方向鉴别信号控制)和MCU选择读取高/低8位计数数据等功能。该电路在XC2C64A-7VC44I器件[5]上进行了下载测试。

图2 绞车信号四倍频、鉴相与计数顶层电路图

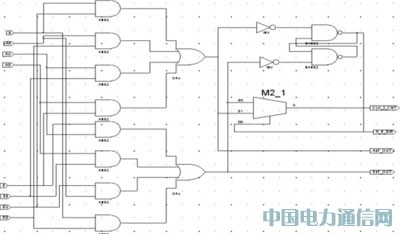

A、B、AA、BB、AU、AD、BU、BD共8路信号经过如图3中左侧所示的倍频电路,产生4倍频的脉冲信号,给后面的计数器提供计数时钟信号;如图3中右上侧所示的由与非门组成的RS触发器,是鉴相(方向鉴别)电路,可以得到反映绞车传感器A、B两相信号到达先后的方向信号A_B_DIR。假设绞车正转,A超前B,A_B_DIR=1;绞车反转, B超前A,A_B_DIR=0。

鉴相(方向)信号A_B_DIR一方面连接到二选一数据选择器的选择输入端S0,用来控制A4F_OUT和B4F_OUT选通到如图2右侧所示的计数器countud进行计数,当A_B_DIR=1(A超前B)时,clk=A4F_OUT(有脉冲输出);当A_B_DIR=0(B超前A)时clk= B4F_OUT(有脉冲输出);同时,A_B_DIR也控制计数器进行加法(A_B_DIR=0)或减法(A_B_DIR=1)计数。

图3 绞车信号四倍频与鉴相电路图

16位二进制加/减计数器的主要功能设计描述如下所示(采用Verilog HDL)。其中,clk是计数时钟输入端,clr是异步清零端,dir是加减计数控制端:dir=1,减法计数,dir=0,加法计数;sel是计数数据读取控制端,由单片机给出的选择信号实现高8位、低8位的计数数据输出,sel=0,低8位,sel=1,高8位。

无线录井绞车倍频、鉴相与计数电路的仿真测试

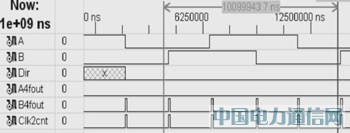

在Xilinx的ISE环境下对倍频、鉴相子模块jch_4f_dir的仿真波形图示于图4。该波形是绞车传感器输出B相波形超前A相波形90°时的仿真结果。此时,倍频输出信号B4fout与A(或B)信号的频率成4倍关系,鉴相(方向鉴别)输出信号Dir=0,这与前面的原理分析完全一致。

图4 B超前A的四倍频与鉴相输出信号波形图

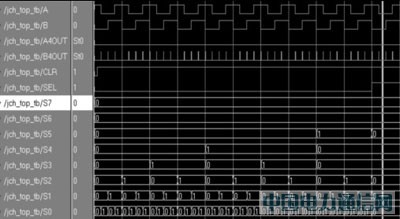

在ModelSim XEIII环境下对绞车检测顶层整体电路(包括倍频、鉴相和计数)的仿真波形图示于图5,该波形是绞车传感器输出B相波形超前A相波形90°时的仿真结果。此时,倍频输出信号B4OUT与A(或B)信号的频率成4倍关系,是计数器countud的时钟输入信号;鉴相(方向鉴别)输出信号A_B_DIR=0,即计数器的加减控制输入信号dir=0,计数器加法计数;单片机提供的数据读取选择信号SEL=0,选取16位计数器的低8位输出,输出的8位数据正是计数器按照四倍频时钟信号进行加法计数的结果。

图5 B超前A的绞车检测输出(倍频、鉴相和计数)波形图

在录井现场,使绞车传感器快速转动产生脉冲,经过电路处理后,传输到主控仪器房的工控机。在设计中考虑现场应用情况,采集到的脉冲计数值是在一个初始值N的基础上变化的(此处常使用30000,即0x7530),正转/反转变化脉冲数在此基础上做加/减运算。绞车传感器转动一圈产生48个脉冲数,现场试验数据分析表明,检测电路对绞车转动圈数的测量非常准确,误差仅是0.01%。

结语

采用一片XC2C64A-7VC44I器件(64个宏单元,33个I/O口,工业级–40°C to +85°C)设计并实现了无线录井绞车信号的检测电路,完成了绞车信号的四倍频、鉴相和16位二进制加减计数以及与MCU数据读取接口等综合功能。录井生产实际应用表明,该设计简化了系统结构,降低了系统功耗,从而提高了系统整体性能,在无线录井数据采集与传输系统中,应用效果很好。

参考文献:

[1] 秦红祥. 综合录井技术在钻井工程中的应用[J].西部探矿工程,2004,67(6):59-60

[2] CoolRunner-II CPLD Family Product Specification.http://direct.xilinx.com/bvdocs/publications/ds090.pdf

[3] 周海骄. 利用CoolRunner-II设计高性能系统[J].微电子技术,2003,31(5):42-44

[4] 王诚等.FPGA/CPLD设计工具-Xilinx ISE 5.x使用详解.北京:人民邮电出版社,2003

[5] XC2C64A CoolRunner-II CPLD Product Specification.http://direct.xilinx.com/bvdocs/publications/ds311.pdf