ժҪ��������һ�ֲ���SoPC�����������ڹ��նȲ����������ͼ��Ҷȹ��ڼ��л����µ���Ƶ��������ʾ��ơ���ϵͳ����FPGA������ͨ����Nios�����˴��������û��Զ�����ģ�顢�洢����I/O�ȼ��ɵ�����ͳɱ���FPGA�ϣ�ʵ�ֶԽ���оƬSAA7113H�ij�ʼ�������á���Ƶͼ��Ҷ��ź�ֱ��ͼͳ���Լ��ҶȾ��⻯��ʵʱ��������ʾ����������ɿ��Ըߣ����ҽ����˳ɱ����ġ�

��ǰ�������˴�������ͼ��ϵͳ�ѳ�Ϊ�о����ȵ㣬ʹ��FPGA����������Ƭ�Ͽɱ��ϵͳ(SoPC)��ͼ����ϵͳ���ѳ�Ϊһ������[1]����ˣ����IJ���SoPC��������Altera��˾��ƬCycloneϵ��FPGA��ʹ��IP��Դ���ü���������NiosII���˴�������������������ӿڣ�����˶���Ƶͼ��IJɼ���Ԥ�������洢����ʾ�����ܡ���ϵͳ��ͼ������˻ҶȾ��⻯������ʹϵͳӦ�ø��㡣����ֱ��ͼ������ֱ�Ӵ���֪��ͼ������ȡ��Ϣ������Ҫ����IJ���˵���������ھ��á����ա���ҵ�������ر��Ǻ���ͼ����ǿ����[2]��ʵ�ʵ����塣SoPC��Altera��˾�������һ������Ч��������ƣ�����Ҫ��Ӳ��[3]���Ϳɷ������չ����Ƕ��ʽ��Ƶ�ɼ����ܡ�ͬʱ�����������ڶ��IP�ˣ���֤����Ƶĸ�Ч�����١�

1 ϵͳ����ṹ������ԭ��

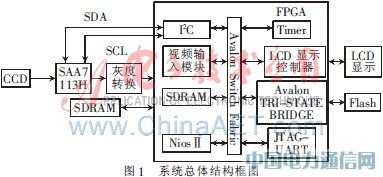

ϵͳ��ͼ��ͼ1��ʾ��ϵͳ�ϵ��Nios II�����е�I2C�������߶���Ƶ�ɼ�ģ��SAA7113H�������ã�FPGA��������ʱ�Ӻ��С����ź�ͬ���ɼ�SAA7113HоƬ�������Ƶ�ź��еĻҶ���Ƶ���ݣ��Ѳɼ����ĻҶ����ݽ��лҶ�ֱ��ͼͳ�ƺͻҶȷֲ����⻯������Nios II�����ⲿ��һ���ӳ�ģ�飬��Ҷ�ת��ģ��������ź�ͬ��֮����Ƶ����ģ�鿪ʼ������ͨ���洢���ơ�DMA������������Ƶ�źţ�LCD��ʾ���Ƶ�ģ����ʾ���ɼ����źš����д�����������ˮ�߲���������ʡ��ϵͳ�Ĵ���ʱ�䡣

2 ϵͳӲ�����

2.1 ��Ƶ����оƬSAA7113H��ʼ��

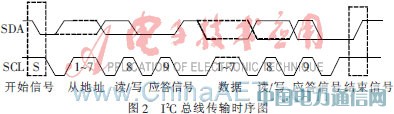

��ϵͳ����Ƶ�������ij�ʼ��������Nios II���˴�����ͨ��I2C������ɣ���Ҫ��������Ƶ�������Ĺ���ģʽ������С���ͬ���ο��źŵ�ʱ���ϵ�Լ���������źŵĸ�ʽ�Ƚ������á�I2C��������Philips��˾������һ�����������ߣ���һ������������SDA��һ������ʱ����SCL��ɣ�����ʵ������ͨ�ţ����оƬ���á����ȣ�I2C���߿���������һ�����ݴ������ʼ������SCL�źű��ָߵ�ƽ����SDA�ź��ɸߵ�ƽ��Ϊ�͵�ƽʱ����ʼ�����ַ����������ʼ�����������һ��8bit���豸�ӵ�ַ�����е���Χ�豸��ʼ��Ӧ��ʼ������ת����һ��8bit�Ĵ�����ַ(7bit��ַ+1bit��дλ)���ɸ�λ����λ���δ��䡣��Χ�豸ʶ��������ַ���ڵ�9��ʱ������(ȷ��λ)�������߱�Ϊ�͵�ƽ��Ȼ��ʼ��8bit����д����߶����Ĵ���(��дλ���������ݵĴ��䷽��)����ʱ����SCLKΪ�ߵ�ƽ����������SDA�ɵ͵�ƽ��Ϊ�ߵ�ƽʱ����ʾһ�����ݴ�����ɣ�ֹͣI2C���ߣ��ȴ���һ�εĴ��俪ʼ��ͼ2ΪI2C���ߵ����ݴ���ʱ��ͼ��

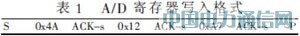

��SAA7113H��4��ģ�������AI11��AI12��AI21��AI22�������Ƶͼ���źţ���A/Dת�����������ɫ���źź������źţ��ֱ���������źŴ�����ɫ���źŴ����������źŴ����Ľ���͵�ɫ���źŴ������������ۺϴ���������YUV�źţ�����ʽת�����VPO(8λ)�����������Щ���ܾ�����I2C���߿�������ɡ�SAA7113�ļĴ�������ͨ��I2C���������У����I2C����Э�顣��1��SAA7113H�Ĵ�����“д”������ʽ��

���У�SΪ��ʼλ��������SCLΪ�ߵ�ƽ��SDA���½��ء�ACK-sΪ�Ӷ��豸Ӧ��λ��PΪ��ֹλ���ڳ�ʼ��������Ҫע�⣺SAA7113H�Ľڵ��ַ(Slave Address)�ϵ硢RTS0Ϊ�ߵ�ƽʱ����I2Cд��ַΪ48H������ַΪ49H��RTS0Ϊ�͵�ƽʱ����I2Cд��ַΪ4AH������ַΪ4BH��

2.2 �Ҷ�ֱ��ͼͳ�Ƽ�����⻯

ͨ������ϵͳ��ȡ��ͼ����Ϣ�к��и��ָ�������������䣬���磬���նȲ������Ȼ����ͼ��Ҷȹ��ڼ��У���CCD��õ�ͼ��A/Dת������·���Ͷ������������Ⱦ�ȣ����ɱ���ػ�Ӱ��ϵͳͼ��������̶ȣ�����ͼ����������ͨ��ͼ����ǿ���Ը���ͼ��������ֱ��ͼ���⻯�㷨�ǿ���ͼ����ǿ��������Ҫ�㷨����ͼ��ѹ����ͼ��ָ��ͼ��ʶ��Ⱥ���ͼ�����Ļ���[2��4]����ͼ��Ԥ�����������й㷺��Ӧ�á�

2.2.1 ֱ��ͼ���⻯ԭ��

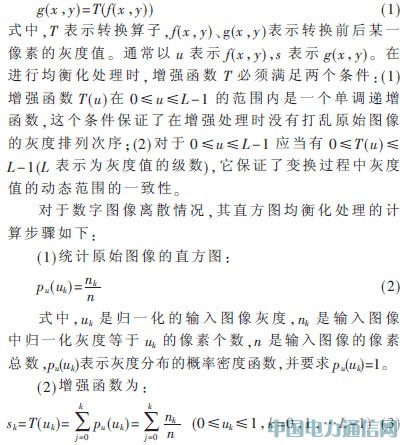

ֱ��ͼ�������Ը�����Ϊ���������ûҶȵ�������ʵ��ֱ��ͼ�任��ԭʼͼ���ֱ��ͼ�����˷ḻ��ͼ����Ϣ��������ͼ��ĻҶȼ����ݣ���ӳ��ͼ��ĻҶȷֲ������ֱ��ͼͳ�Ƽ����⻯�Ļ���˼���Ƕ���ͼ�������ظ�����ĻҶȼ�����չ�����������ظ����ٵĻҶȼ������������Ӷ��ﵽ����ͼ���Ŀ��[5]��ͨ��������ʹ����ͼ��ת��Ϊ��ÿһ�Ҷȼ��϶�����ͬ�����ص����Ŀ����ͼ����ǿ�������������¹�ʽ��

(3)���ۻ��ֲ��������任��������ͼ��Ҷȱ任��

2.2.2 ����FPGA���㷨�Ż���ʵ��

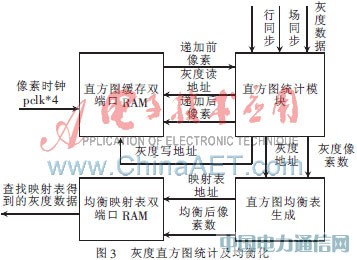

�㷨�Ĺؼ�����FPGA��ʵ��ֱ��ͼͳ�ƺ;�����ӳ���ϵ��������Ʋ���FPGA�����ṩ��Block RAM�����ֱ��ͼ�;����ӳ���ϵ������˫�˿�RAM������ṹΪ���ģ��������㷨��Ϊ��������ִ�У�(1)ͳ��ԭʼͼ��ĸ����Ҷ�ֵ��������Ҷȼ�����RAM�У�(2)�Եõ��ĻҶ�ֵ���Ҷ�ӳ�䣬��ӳ���Ľ�����뵽ӳ���RAM�У������ɾ���ӳ���������ӳ����Ϳ���֪��ԭʼͼ��ijһ�Ҷȼ������任��ĻҶȼ������������Ĵ������Ϳ���ԭʼͼ�����ܼ��ֲ��ĻҶ�ֵӳ�䵽����ֱ��ͼ���⻯����µĻҶȼ��ϡ�ͼ3Ϊ���㷨������ͼ��

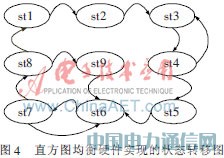

���ǵ�FPGA��Ӳ���ص㣬�ڽ���ͼ�����ݡ�����˳���ֱ��ͼʱ����FPGA��ʵ�ָ���������������Ը��������Ľ϶�����Դ������ڶ�ͼ�����ֱ��ͼͳ��ʱ�����Ҷȼ����ص�ĸ�����Ϊֱ��ͼ���ݣ�pu(uk)=nk���Ա���ʹ�ø������������㡣��ֱ��ͼ���о��⻯�������õ�ԭ�Ҷȵ����⻯��Ҷ�ӳ���ϵ����������е�ֱ��ͼ���⻯���㷨�����״̬ת��ͼ��ͼ4��ʾ��������ת�������������ź���Чʱ����st1ת��st2����������1������255ʱ����ת��st3����������1û�м�����ͼ��߶ȼ�1��������2û�м�����ͼ����ȼ�1ʱ����ת��st3����������1������ͼ��߶ȼ�1�Ҽ�����2������ͼ����ȼ�1ʱ����ת��st5����������1û�м�����255ʱ����ת��st6����������������255ʱ����ת��st7����������1������ͼ��߶ȼ�1�Ҽ�����2������ͼ����ȼ�1ʱ����ת��st1״̬����������1û�м�����ͼ��߶ȼ�1��������2û�м�����ͼ����ȼ�1ʱ����ת��st6���ڽ��м���ͳ��ʱ���������ڼ��õ�һ�����ص�ĻҶ�֮����Ҫ��Ӧ�ؽ���������1�����Ҷ�Ӧ�Ҷ�ֵ���ڵ�ǰ�Ҷ�ֵ�����м���������1����������ͬʱ���ԭʼͼ������ػҶ�ֵ��ͳ�ƺ��ۻ���������ͳ��ʱ�䡣

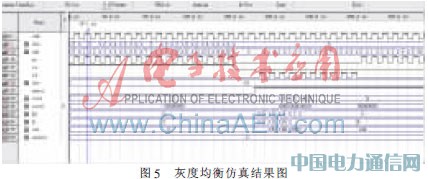

��Ϊ�ڻҶȾ�������������Գ�Ϊ��λ���еģ��ڻҶȾ��⻯������֮��Ҫ�����ϲ�Ϊ֡�����������Nios II�����е�SDRAM�������������ż���ĺϲ����ҶȾ��⻯�ķ�����ͼ��ͼ5��ʾ��

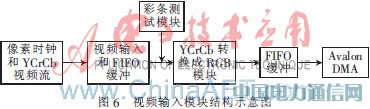

3 ��Ƶ����ģ��

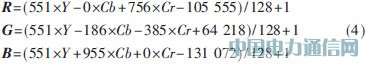

��Ƶ����ģ��Ľṹʾ��ͼ��ͼ6��ʾ�������Ҷȱ任YcrCb4��2��2��ʽ��Ƶ�ź�������ʱ�ӿ���������FIFO�����������������ź�ģ����ϵͳ����ʱ������һ���dz��IJ����źţ�����ģ��Ϊ�ź�Դ���Է���ϵͳ�ĵ��ԡ�ɫ��ת��ģ�齫YCrCb��ʽת��ΪRGB��ʽ��������ֵд��FIFO�������С�Avalon DMA��ͼ������д��ϵͳ�洢��(SDRAM)�У������һ֡ͼ����д����ʱ����Nios II������һ���ж��źš�

��ɫ�ȿռ��ת��ģ���У�����FPGAƬ�ڵ���Դ������MegaCore����һ���˼�����������㡣����ת��������YUV�ı�����ϵ�����źŷŴ�һ���ı�����ʹ��ӽ�һ������ֵ��YUV�źŵ����ֵΪ255������10bit DATA���Խ���1 023���ȵȼ��ĵ��ڣ���������������ԷŴ�4������(�������1023�Ͱ�1023�ĵȼ�����)�����ݷ���ʵ�����ó����������µ����������ӽ�ת������

4 Nios IIϵͳ������

��SoPC Builder���Խ���ϵͳģ��Ӳ����ƺ͵ײ��������ɡ�����Ӳ��ģ�����ʱ��SoPC Builder�ṩ��ͼ�λ����ý��棬����һЩ���������IPģ�飬��SDRAM��Flash RAM��UART��Interval timer��Parallel I/O�ȡ�Nios II���������������ͼ7��ʾ��

��SoPC Builder�Դ���IP�˿��в�û��I2C����ģ�顢��Ƶ����ģ���LCD controllerģ���IP�ˣ���Щģ���Ǹ��ݼĴ����ص��Լ�����Ҫ��������Ƶģ�����IP�˵���ʽͨ��Avalon�������ӵ�SoPCϵͳ�ϡ��ڽ����˻���Nios II��������SoPCϵͳ����Ҫ����һЩϵͳ���ò����������յ�Nios IIϵͳ����ˣ�ϵͳ���ó��˶����������⣬���������������ж���������ϵͳ������ַ�ȵ����á�

���Ľ����˻���SoPC��������Ƶ�ɼ������Լ�����Ƶ�źŽ��лҶ�ֱ��ͼͳ�Ƽ��ҶȾ��⻯��ʵ�֡��÷������SoPC��������Ӳ���ɲü�������������������ŵ㣬���������ϵͳ����������ڣ��кܺõ�Ӧ��ǰ���Ϳ��м�ֵ��

�����

[1] ���գ�����.����FPGA��SoPCǶ��ʽϵͳ��������ʵ��[M].���������ӹ�ҵ�����磬2009.

[2] ���ӣ������ܣ���Ⱥΰ����.����FPGA��ֱ��ͼ����ʵʱ�����㷨���¼ܹ�ʵ��[J].���⼼����2010(3).

[3] ����Ӣ.NiosIIǶ��ʽ����SOPC���ԭ����Ӧ��[M].�������������պ����ѧ�����磬2006.

[4] �Ƴ��䣬��᷽���ο��ã���.�Ľ���ֱ��ͼ����ͼ����ǿ�㷨��ʵ��[J].��Ϣ��ȫ��ͨ�ű��ܣ�2009(12).

[5] ³��.����FPGA��ʵʱͼ��ֱ��ͼ������ǿ���[J].����Ӧ�ü�����2006��32(11).