摘要:介绍一种采用单片SRAM和FPGA实现红外图像显示的新方案,并对显示系统结构、FPGA各功能模块设计、SRAM的读/写时序设计进行了详细论述。该图像显示方案可用于红外图像处理系统的硬件调试和红外图像处理效果观测。实际使用情况表明,该显示方案能够很好地满足红外图像处理系统的图像输出需求。

随着红外探测技术的发展及其在军事、工业等领域的广泛使用,红外图像处理算法获得了广泛研究。在实际嵌入式红外图像处理系统中,为了方便硬件调试和观察图像处理的效果,需要在系统中加入图像显示模块。通常视频数据流需要处理的数据量大,实时性要求高,所以需要高速大容量的存储器作为图像数据的缓存。用于图像数据缓存的存储器有3种:①同步动态随机存取存储器SDRAM(Synchronous Dynamic RAM),其容量大、速度快、体积小、价格低,但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,需要设计专门的SDRAM控制器以完成与SDRAM芯片的接口;②双口RAM,它可以同时对数据进行读写,时序简单,操作非常方便,但是容量相对较小,而且价格高;③静态随机存取存储器SRAM(Static RAM),它不仅容量大、速度快、体积小、价格低,而且时序控制简单,但是数据不能同时读写,工程中多采用2片SRAM做乒乓操作来简化读写控制。针对实际工程中的体积小、成本低、开发周期短等要求,本文提出一种基于单片SRAM和FPGA的图像处理及显示方案,并在实际工程中得到了应用。

本文的初始设计是面向帧频为50帧/s、16bit灰度、图像为320×256像素的红外图像输出显示,但其设计方案可以应用于不同帧频、灰度级及图像大小的图像显示。

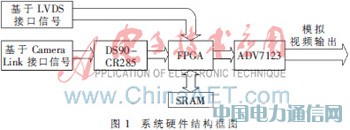

1 系统硬件结构和工作原理

系统硬件结构图如图1所示。本系统中,高速串行LVDS视频信号经Camera Link接收芯片DS90CR285接收转化为并行TTL电平后送给FPGA,同时,其他系统的高速串行LVDS格式数据也可以直接送至FPGA。这些视频数据经FPGA进行直方图统计,并存储在SRAM中。然后,FPGA在存储间隙读出SRAM内的有效像素数据,并采用直方图统计的参数对图像灰度拉伸,然后送至视频转换芯片ADV7123进行D/A转换显示。

2 各功能模块设计

2.1 Camera Link接口

本方案选用DS90CR285将Camera Link格式的4对串行LVDS图像信号转换成28bit并行TTL/CMOS的数据。根据Camera Link基本协议,28bit数据信号中包括3个数据端口:A口(8bit)、B口(8bit)、C口(8bit),和4个视频控制信号FVAL(帧有效)、DVAL(数据有效)、LVAL(行有效)、SPARE(空,暂时未用)。经过Camera Link芯片转换后的时钟信号是整个相机的同步驱动信号,所有的数据和视频控制信号都和该时钟信号同步。数据转换后送入FPGA的时序如图2。

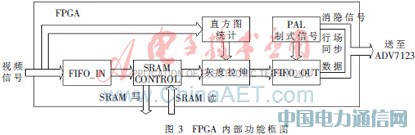

2.2 FPGA核心功能模块实现

本设计中视频数据的处理都在FPGA内实现,其内部功能框图见图3。

本文主要讨论在FPGA内,利用视频数据的行场扫描间隙对单片SRAM进行读写操作从而完成模拟图像的显示功能。直方图统计功能在另文中描述。

本系统中,视频信号时钟为20MHz,PAL制式信号数据时钟采用13.5MHz。为了让SRAM读写时间更加充裕,使用了两个FIFO模块作为数据缓冲:FIFO_IN、FIFO_OUT。FIFO_IN用来做SRAM的输入缓冲器,FIFO_OUT用来做SRAM的输出缓冲器。FIFO可以通过IP核来实现,存储宽度为16bit,存储深度设置为1.5倍行像素,本系统为1.5×320=480[1-2]。

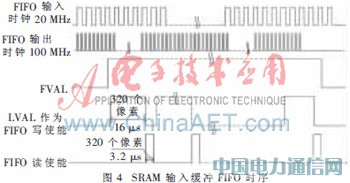

2.2.1 FIFO_IN模块

为保证数据读写效率,此模块的读写方式需进行合理规划,具体为每次往FIFO中写一行数据,写完后立刻从FIFO读一行数据并写入SRAM。像素时钟为FIFO的写时钟,行有效信号作为FIFO的写使能,FIFO读时钟为100 MHz,也是SRAM的读写时钟,通过判断行下降沿来生成一个320的计数器,并在计数器有效期间将FIFO读使能置为高。FVAL的上升沿作为FIFO的复位信号。此FIFO的读写时序图见图4。

2.2.2 FIFO_OUT模块

此模块主要是缓冲灰度拉伸后的视频数据用于输出显示。本系统要求输出标准的PAL制式的模拟视频,PAL制式视频场频为50Hz,帧频为25Hz。本方案选用专用的图像DA芯片ADV7123, 该芯片是一款高速的RGB D/A转换芯片,内部集成有3路10位精度的D/A转换器,分别用于RGB数字信号的D/A转换,数据吞吐率可达到330MS/s,适合高分辨彩色视频生成。ADV7123提供有3路数字输入接口(RE9:0]、G[9:0]、B[9:0])以及CRT消隐和同步控制信号(BLANK、SYNC)。标准PAL制式的行场消隐信号和行场同步信号都是标准信号,在FPGA内很容易实现,本文不再论述。实际应用中只需要在需要显示图像的正确行场位置,将图像灰度数据送入G[9:0]通道,即可在lOG端口得到复合视频信号。同时这些正确行场位置标志信号作为FIFO的输出使能,输出时钟为13.5MHz,输入时钟为100MHz,输入使能为灰度拉伸模块的输出数据有效信号,输入数据为灰度拉伸模块的输出数据。FVAL的上升沿作为FIFO的复位信号。

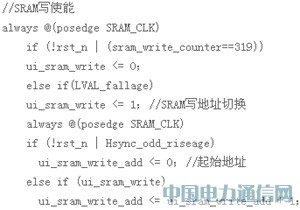

2.2.3 SRAM读写控制模块

SRAM作为视频数据的缓冲区,根据上述时序其容量最好能大于2帧数据,同时为了便于以后扩展,本方案中选用SRAM为CY7C1472BV33,容量为4M×18bit。由于SRAM属于单向存储器,利用单片SRAM作存储的难点在于如何将读写控制分开。此控制包含2部分:读写使能和读写地址变换。下面分别从读和写来说明这2部分控制的实现。

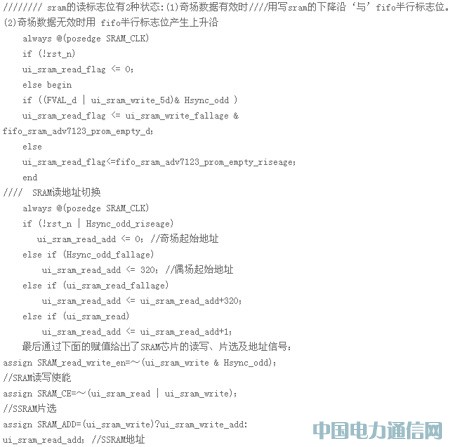

FIFO_IN的读使能作为SRAM的写使能,写地址在写使能有效期间从SRAM的零地址依次递增,即地址范围为0~81919(320×256-1)。但由于本系统中视频信号20ms一帧,PAL制式视频显示一帧需要奇场20ms、偶场20ms,共40 ms,所以在偶场显示时还是在读SRAM中0~81 919部分的数据,此时视频信号必须写入SRAM的另外一部分空间,这就要求在奇场和偶场时写地址要进行切换;或者采用在奇场时数据写入SRAM,偶场时不写入,这样刚好做到显示完一帧图像,下一帧图像数据就可以覆盖上一帧图像的数据,这样写地址就一直是从0~81 919,不需要切换。本方案采用后者,其写使能及写地址的FPGA主要代码如下:

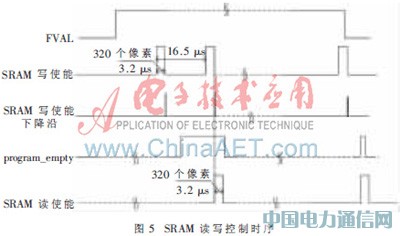

SRAM的写使能设计要避免与SRAM的读使能冲突。本方案在FIFO_OUT模块上设计了一个可编程空标志位program_empty,当fifo数据不足160个时,program_empty置高,PAL制式视频的行扫描周期为64μs,也就是FIFO_OUT每64μs被读一次(一次读出320个数),这样只要在64μs时间内能够写入320个数就可以保证下次行扫描能够从FIFO_OUT取出数据。由于本系统中SRAM的写使能周期为16.5μs,因此本方案是将SRAM读状态分2种情况,在FVAL信号有效期间,采用program_empty置高和SRAM的写使能下降沿的“与”操作作为SRAM读触发信号;在FVAL信号无效期间,SRAM无写控制,program_empty信号的上升沿将作为SRAM的读触发信号。然后根据读触发信号生成一个320的计数器,并在计数器有效期间将SRAM的读使能置为高。这样就能保证SRAM的读写不冲突,且数据也不会漏写,控制时序见图5。

PAL制式视频显示分为奇场和偶场,因此在奇场时,SRAM的读地址应该满足:第n行地址范围为320×(n-1)~319+320×(n-1)(n=1,2……128);偶场时,RAM的读地址应该满足:第n行地址范围320×n~319+320×n(n=1,2……128),其读使能及读地址的FPGA主要代码如下:

2.2.4 灰度拉伸

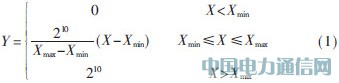

将SRAM的读使能和读数据送入灰度拉伸模块作为数据使能和输入数据。本方案中,图像灰度线性拉伸算法表达式为:

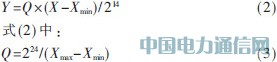

式(1)中:Y是拉伸后输出图像灰度值;X是SRAM中读出的数据,为原始图像16bit二进制数灰度值;Xmin是输入图像数据直方图统计最小灰度值;Xmax是输入图像数据直方图统计最大灰度值。为保证精度,实际应用中将上述公式进行简单变换,可以记为:

Q值在上帧结束前直方图统计模块已经得到,这样拉伸运算只需1次减法和乘法运算,得到积左移14bit后,截取低10bit就得到拉伸后的灰度值。需要注意的是,截取前要判定乘法是否溢出,如果溢出,结果置为最大灰度值210。本方案中主要通过调用乘法器IP核来完成乘法运算,不同硬件的乘法器延迟时间不同,所以必须要将输入数据使能信号作相应延迟后,成为输出使能与乘法器输出数据同步[3]。经过灰度拉伸后的图像数据送入FIFO_OUT模块用于图像显示,其中,灰度拉伸模块的输出使能及输出数据作为FIFO_OUT模块的输入使能和输入数据。

该图像处理方案以FPGA 作为核心控制芯片,采用单片SRAM实现了图像预处理、数据缓存、图像存储及显示的功能。随着FPGA 性能的不断提高及其灵活的可编程性,设计者可以进一步在FPGA内部实现各种其他的图像处理算法。这样,直接采用FPGA和单片SRAM的方案不但减小了PCB 尺寸,降低了元件数量及PCB布线的难度,也降低了元件相互连线带来的信号失真,从而增加了可靠性和稳定性。本方案已成功应用在本单位的图像采集和处理产品中。

参考文献

[1] 田耘,胡彬,徐文波,等.Xilinx ISE Design Suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[2] Xilinx Corporation.fifo_generator_ds317.http://www.xilinx.com,2005.

[3] Xilinx Corporation.Muli_gen_ds255.http://www.xilinx.com,2005.