��������������Ƶ���ϵͳ�����С����ٹ�·��¥��ȸ�������ȡ���˹㷺��Ӧ�á���������Ƶ���ϵͳ�У�OSD(On Screen Display)�����Dz��ɻ�ȱ�IJ��֡�OSDΪ�û��ṩ�Ѻõ��˻����棬�ܹ�ʹ�û���ø���ĸ�����Ϣ��

ϵͳ����

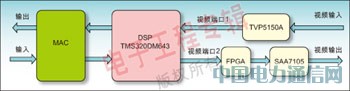

���Ľ��ܵ�ϵͳ�ǻ���TI DSP TMS320DM643��FPGA��������Ƶ���ϵͳ��֧��1·��Ƶ�������1·��Ƶ���������ṩ����ӿڡ�

��Ƶ�������TI�ĸ��Լ۱���Ƶ������TVP5150A��ʵ�֣�TVP5150A��ʵ����·������Ƶ�����һ·S-video��Ƶ�źŵIJɼ���ͨ��I2C���мĴ������ã����������Ƶ�ź���ѭITU656����

TVP5150A������������Ƶ�ź�ͨ��DM643����Ƶ�˿�1����DSP����DSP���б�Ҫ����Ƶ������������ӿ������Զ���豸����һ���棬DM643�Ѵ�������յ���Ƶ���ݴ�����ͨ����Ƶ�˿�2������FPGA����SAA7105��ʾ���������ṹ��ͼ1��ʾ��

������ֲ���SAA7105ʵ�֡�SAA7105��NXP��˾��һ���������Ƶ�����������ṩ������Ƶ�����VGA��Ƶ����Լ�HDTV������Ƶ�źŵ������SAA7105�Ŀ���Ҳͨ��I2Cʵ�֣����ո���ITU656����������Ƶ�źš�

��Ƶ�������ֲ��õ���TI��DSP TMS320DM643��ʵ�֡�DM643��Ƶ�ɴ�600MHz����2��20λ����Ƶ�˿ڣ���Ƶ�˿�֧��BT.656��Y/C��������Ƶ�ӿڣ�DM643������������MAC����ʵ��������롣

Ӳ�����ܵķ�չ�ٶ����Ǻ���������������������Ƶ����Խ��Խ���ӵ�Ӧ���У�DSP�е��ŷ��ӵ���Ƶ����������Դ��÷dz����ţ������ڱ�ϵͳ����У�������FPGAʵ��OSD����ƣ����Լ���DSP�ĸ�����

OSDʵ�ֲ���ѡ�õ�������˼��˾��XC3S250E��XC3S250E������˼SPARTAN-3Eϵ�е�FPGA����25������š�

ͼ1 ����TMS320DM643��FPGA��������Ƶ���ϵͳ�ܹ�ʾ��ͼ

OSDʵ��

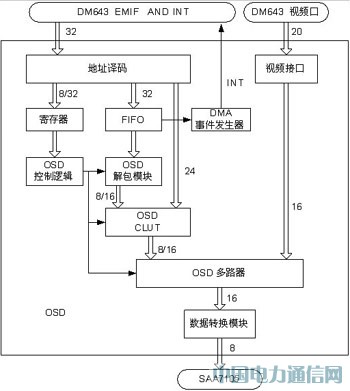

SAA7105��ʵ��OSD���ܣ�����XC3S250E��ʵ�֡�����оƬDM643ֻ��Ҫ֪ͨFPGAҪ��ʾ�����ݺ�λ�ã�����Ĺ�����FPGAִ�С�OSD������ͼ��ͼ2��ʾ��

ͼ2 OSD���ܿ�ͼ

OSD FPGAͨ��EMIFA��DSP DM643����OSD���ݺͿ���ָ�ͨ��DSP����Ƶ�˿�1������Ƶ���ݣ�����OSD����Ϣ���ӵ���Ƶ�����ϣ��������Ƶ������SAA7105��OSD�ĸ�����ģ���������¡�

��ַ����ģ������ݶ˿���DSP DM643��EMIFA��32λ���ݽӿڣ�����DM643�����������������Ϣ����Щ���ݺͿ�����Ϣ��DM643������ԭʼ32λ���ݡ���ַ����ģ�齫���յ���OSD���ݣ���OSD�����ݵȣ���32λ���ݸ�ʽ���뵽FPGA���ڲ�FIFO�С���������Ϣ��Ҫ��ͨ��һ����ƼĴ�����OSDʵ�ֿ��ơ�

��DSPֱ�����ӵ�ģ�黹����Ƶ�ӿ�ģ�顣��Ƶ�ӿ�ģ����DSP����Ƶ�˿�2�������洢����DSP��Ƶ�˿ڵ������������Ϣ����Щ������Ϣ��ֱ�Ӵ����OSD��·����ģ�飬ͬʱ������ϢҲֱ�ӿ�����Ƶ������SAA7105��

OSD�������Ѵӿ��ƼĴ�����õ��Ŀ�����Ϣ�����OSD�ĸ�������ģ�飬ʵ�ֶ�OSD�Ŀ��ơ��Ĵ�������Ҫ��Ϊ�������֣�һ���첽�Ĵ����飬��OSD�����縴λ��OSDʹ�ܺ�ѡ�����ݿ��ȵĿ�����Ϣ����һ����ͬ���Ĵ����飬��Ҫ����OSD��λ����Ϣ��

OSD����ģ����ݿ������Ŀ�����Ϣ����FIFO��ȡ��Ҫ��ʾ�����ݣ�������Ƶ����ͬ���ķ�ʽ�����OSD CLUTģ�顣��FIFO�л�õ�������ԭʼ��DSP 32λ���ݣ���OSD CLUTģ����Ҫ��������8/16λ�ģ�����OSD���ģ����Ҫ��һ���Ĺ���32λ���ݽ��������Ƶ�˿ڵ�Ƶ�ʽ�32λ������8/16�Ŀ��ȴ����OSD CLUTģ�顣

FIFOģ�������һ����������DMA�¼�������ģ�鴫��FIFO��״̬��Ϣ����FIFO����FIFO�ա�DMA�¼������������Щ�¼�����������������жϵ�ģʽ����DM643����ʵ�ֶ�FIFO����ȷ��д������

OSD CLUTģ��Ϊ��OSD���ģ����յ�ÿ�����ص����ݲ���YCbCr�Ķ�Ӧֵ����������ЩOSD CLUT���ݵ����˳������ת����ϵ����DSPͨ��24λ�����ݶ˿ڴ������ġ�OSD CLUTģ�������ֱ�������OSD��·������ģ�顣

OSD��·����ģ����ݴ�OSD CLUTģ����յ���Alpha����λȷ�������Ƶ���ݣ������ǰΪOSD��Ϣ����Alpha����λ��Ч�������OSD���ݸ�����ת��ģ�顣�����������Ƶ�ӿ�ģ����յ�ԭʼ��Ƶ���ݣ��Դ���ʵ��OSD���ܡ�

OSD��·��������������ݲ�û��ֱ������Ƶ������������ͨ������ת��ģ�飬���ݾ����Ӧ�����������б�Ҫ�����ݸ�ʽת������SAA7105�Ľӿ�ʱ���֪����SAA7105����Ϊ������Ƶ���ʱ����Ҫ�������Ϊ��ʱ�������ݣ���ʱ����ת��ģ�鲻���κι���������OSD��·����ģ����յ�����ԭ�ⲻ���ش����SAA7105�����SAA7105����ΪVGA��HDTV���ģʽʱ����Ҫ˫ʱ�������ݣ���ʱ����ת��ģ�齫��OSD���������յ��ĵ�ʱ��������ת����˫ʱ�������ݣ��������Ƶ������SAA7105��

�ɴ˿ɼ���FPGA�����OSD�����й��������Ҫ��ʾOSD���ݣ�DM643ֻ��Ҫͨ��EMFIA����FPGA���Ϳ���ָ��ɣ���Щָ�Ȼ����OSD�����ݼ�λ����Ϣ��

OSD����

��XC3S250Eʵ�ֵ�OSD��Ƹ��ݽ��յ���OSDλ�ü�������Ϣ����OSD��ʾ����OSD��ʾ������û���κ����ƣ��dz����㡣������OSD������ʾΪ��˵��OSD�Ŀ��Ʋ�����

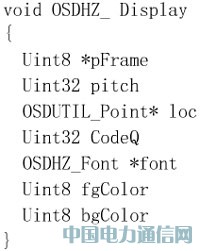

Ҫ��ȷ����ʾ���֣��ͱ��뽫����ĺ�������ת���ɶ�Ӧ����λ�롣��һ��������ͨ������Uint32 Code_Converse(unsigned char *CodeNPointer)��������Ϊָ�룬ָ��Ҫת�����֡�����ֵΪ�ú��ֶ�Ӧ����λ�롣OSD����ʾ�ɺ���OSDHZ-Displayʵ�֣�

���У�Uint8 *pFrameΪOSD�����Buffer��������Uint32 pitchΪÿ����ʾ������ֵ��OSDUTIL_Point *locΪ��һ���ַ�����ʾλ�ã�Uint32 CodeQΪҪ��ʾ���ֵ���λ�룻OSDHZ-Font *fontΪ��ʾ�������õ����壻Uint8 fgColor��ʾ���ֵ�ǰ��ɫ��Uint8 bgColor��ʾ���ֵı���ɫ��

���ԣ������Ҫ��ʾ���֣�ֻ��Ҫ�����ֽ��б�Ҫ������ת����Ȼ��ת�������λ�룬������ʾ��λ�ã������OSD FPGA���ɡ���ȻҪ��ʾ���֣������ֿ��DZز����ٵġ�