����

����ͼ��������Ӧ�õ��ռ�����Ӧ�÷�ΧԽ��Խ�㡣��ҽѧ�����¡������������ر��ǽ�Щ���ڹ�ҵ�Զ�������ҵ��ⷽ��õ��㷺Ӧ�á�Ŀǰ��ͼ����ϵͳ�����ü����������Ƶ�ɼ���������ͷ��������Ӳ��ϵͳ������Ӳ���ṹ���ڴ������������ӵļ���ͼ����ϵͳ��Ȼ�Dz����ʵġ�

Ŀǰ��EPLDоƬ�ڲ�����ԴԽ��Խ�࣬�ٶ�Խ��Խ�죬��������������Ҳ�������ƣ�ʹ��Ӧ�������������ձ���Ϊ�������������ϵͳ������CPU+RAM+EPLD�ĽṹΪ������ͼ��ϵͳ����С�ͻ���չ��������һ�ġ��ͳɱ���ͼ����ϵͳ�ǽ�ͼ��������Ӧ�õ���������������Ҫ��

���Ľ��ܵ�ϵͳ���������������������������ġ�

1 ������Ʒ���

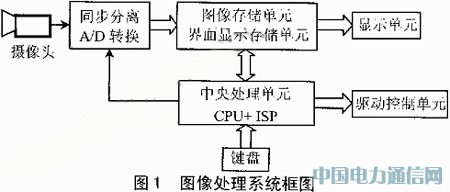

����ϵͳ������ͷ��ͼ�����뵥Ԫ��ͼ��洢��Ԫ��ͼ������Ԫ��ͼ����ʾ��Ԫ���������Ƶ�Ԫ��������ɡ�ͼ����ϵͳ��ͼ��ͼ1��ʾ��

��ͼ����ϵͳ����Atmel��89C55Ϊ���봦����Ԫ��ϵͳʱ��Ϊ20MHz��ͼ��ɼ�������ISPLSI1032E�ṩ�洢ͼ��RAM�ĵ�ַ�źźͲɼ�ͼ������ʱ���źš�������Ҫÿ֡ͼ��ɷ�Ϊ256×256��512×512���������������Ҳ�ɲ���256×128��512×256������ʽ����ͼ�������Ԫ���ɽ�ͼ������ʾ�˵�������������ɿ��Ӳ˵���

���⣬Ϊ��Ӧ��ҵ����ҵ�Զ��������Ӧ�ã���ϵͳ�л�������������Ƶ�·�����������������ģ�������������ܹ���Ӧ���ֿ��Ƴ��ϡ�

2 Ӳ����·���

2.1 ISP��������

ISP����������һ��PLD���������е������ԡ������ܺ�FPGA������ԡ����ܶ��⣬����Ҫ��һ����������ϵͳ�ɱ�̼�������ISP�����ڿհ�״̬�º��ӵ���·���ϡ��κ��Ѿ���װ��ISP�����ĵ�·�壬ֻҪͨ��PC�������ص��£����������µı�̴��룬����һ�й������ڲ��ϵ��ǰ���½��С�

ISP(In SYSTEM PROGRAMMING)������LATTICE�뵼�幫˾�����ṩ������һ�����ڲ�Ʒ��ơ���������е�ÿ�����ڣ������ڲ�Ʒ���������û��Ժ���ʱ������������·�����������ϵͳ�������ܽ�����̬����������¼�����

��ϵͳ���������У�ͼ��ɼ��ĺ��IJ�������Ƶ�źž�A/Dת���Ľ����δ洢���洢���У�����θ�����Ƶ�źŲ����洢���ĵ�ַ�źš��������������������Ĺ��㣬���Dz���ISPLSI1032Ϊ��ַ������������һЩ����·��

2.2 ͼ��ɼ�ʱ��IJ���

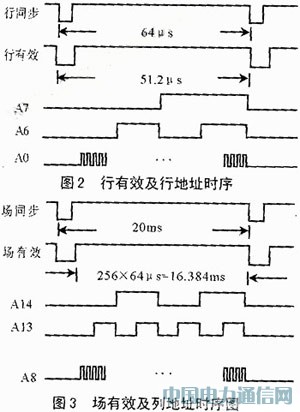

�����256×128����Ϊ����˵��ͼ��ɼ�ʱ��IJ�����

��A0��A7��ʾÿ���е���ĵ�ַ��A8��A14��ʾ�е�ַ��������Ч�źź�A0��A7��ַ��ʱ����ͼ2��ʾ���䳡��Ч�źź�A8��A14��ַ��ʱ����ͼ3��ʾ����������256×128=32768���洢��Ԫ�洢1��ͼ��

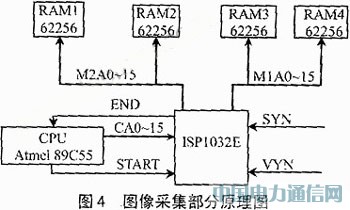

�����Ҫ�ɼ�ͼ������CPU��ISP����START�źţ���ISP�Ͽ�CPU�ṩ��ͼ��RAM�ĵ�ַ�ߣ�����ISP����ͼ��RAM�ĵ�ַA0��A14��SIP������1��ͼ��ĵ�ַ�����1��END�źţ�֪ͨCPU��ͼ��ϣ����ó�RAM�ĵ�ַ�ߺ������߸�CPU���������ͼ������

ϵͳ*��4Ƭ32K×8bit��RAM(62256)�����У�

RAM1Ϊͼ��֡�棻

RAM2Ϊͼ�α�־λ������ͼ��ı�ע��

RAM3Ϊ�˵�������Դ棻

RAM4Ϊϵͳ�ڴ棬�����洢�������м����ݺʹ��������

ͼ4Ϊͼ��ɼ�����ԭ��ͼ��

��ʵ��ʹ���У�CPU��RAM1��RAM4��RAM2��RAM3�IJ����Ƿ�ʱ���еġ���ɨ���ڣ�CPU��RAM1��RAM4���в���������ͼ��ļ���ͽ�����������ڻ�ɨ�ڣ�����в˵��ͱ�ע��ˢ�¡�ISP��RAM2��RAM3�IJ�������ɨ���ڣ����в˵��ͱ�ע��ͼ��ĺϳ������

ISPEXPERT��LATTICE��˾��20����90���ĩ�Ƴ���һ��������ISP���ɿ�������������500����Ԫ���ɹ����ã�֧��VHDL��Verilog-HDL��ABELHDL��ԭ��ͼ������һ��Ŀ���������������ISP����������ƺ��Ż�����ӳ�䡢�Զ����ֲ��ߡ�������˿ͼ�ļ��ͱ�����ء����⣬�������Զ���Ƶ�����ϵͳ���й��ܷ��桢ʱ�����;�̬ʱ�������

��ʹ���ߵĽǶȿ���ISPEXPERT��Workview office��Synario�������ܸ�ǿ���������㡣

��ϵͳ����ISP1032EоƬʡ���˸��ӵġ�����������·������VHDL���Ա�̣�ͨ��ISPEXPERT���ɿ��������������Ƚ�ʡ�˴�����Ӳ������ʱ�䣬�ּ�������·�������š�����Ҫ���ǽ�ʡ���ظ��ư��ʱ�䣬��������˲�Ʒ�������ڡ�

������

����ISP�͵�Ƭ�����ɵ�ͼ����ϵͳ�����нṹ�����ɶȸߡ����С���۸�������ص㣬���������ھ���ͼ�������ܵ�Ƕ��ʽϵͳ�Ŀ�������ϵͳ����ʵ����ʹ�ã�ȡ�������õ�Ч����