ժҪ����������FPGAΪ����оƬ���Թ��ΪͨѶý�����Ƶ�ź�����ͨ��ʵ��װ�õ����ʵ�ֹ��̣����Ե�·����ģ��Ĺ��ܼ�ʵ�ּ���˵������·��altium designer�������ɣ����÷�ģ��ʽ����ƣ�˼·���ṹ����������ʵ�֡���Quartus������VerilogHDL���Խ��б�̲��Գ�����з��档��װ����������ʵ��������ʵ��ʹ�ñ���������ʵ����Ƶ�źŵĴ��䣬�ﵽ�������Ľ�ѧҪ���ʵ��Ч����

��������Ƶ������������˥��С���ŵ��ͨ����������ĸĸ�ʹ��£��γ���һ�����˲�ҵ������ͨ�ŶԱȴ�ͳ��ģ��ͨ���п���������ǿ�����÷�Χ�㡢��������ǿ�����ڼ��ɡ������ȶ����ŵ㡣���ֹ���ͨ�ż������ߵ��ŵ㣬�ؽ���Ϊͨ������ķ�չ����

��Ƶ�źŵĹ��˴�����ʵʱ��ȷ���������ŵ㡣��ʵ�������Կ���ȷ�ش���ʵ��ͼ��ʵ���߸��ɿ�����Ϣ���ڼ�ط��棬����ʵʱ���ݼ��ͼ����Լ�ɱ������иߵĴ�����������ˣ���Ƶ�źŵĹ��˴�����о���ʵ�֣����������ǵ�ѧϰ�����������

�����������ͨ�������У�У���ͨ������Ϣ����רҵ��ѧ�ƣ������ռ���ʵ���ѧ��Ŀ�����ƵĴ���ʵ���ѧ��������ʵ���������Ƴ��������ڰ����ߵ�ѧУ������ѧ��ʵ��γ̵��������ḻ������ʵ������ݣ�ʹѧ���˽��ִ������ķ�չ�����֪ʶ�����ա�

1 ϵͳ��Ӳ���ṹ

����װ����������ɣ���������ⷢ����������֮���Թ������ӡ��ⷢ�������������Ĺ���ԭ���������һ������һ��������̣��ⷢ�����ǽ���Ƶ�ĵ��ź�ת��ɹ��źţ���������ǽ����ź�ת�����Ƶ�������š�

�ⷢ�������˲��Ŵ�A/Dת�������Ʋ��֡���/��ת������/��ģ�鲿����ɡ�

��������ɹ�/��ת�����֡���/��ת�������Ʋ��֡�D/Aת����ģ���źŷŴ���ɡ�

2 ϵͳ��·���

2.1 ��Դ

����װ�ý���7.5 Vֱ����Դ���磬�ڲ����ɵ�·���õ�5V��1.5V��3.3V�ĵ�Դ��5V��Դ��L7805��̬��ѹ��Դ�ṩ��3.3V��1.5V�ֱ���ASM117-3.3��ASM117-1.5�ṩ��

2. 2 FPGA���ز���

��·�����ͺ�ΪEPIC3144C8��FPGAΪ����оƬ����32 MHz�ľ����ṩ����ʱ�ӡ�оƬ����4��ʱ������ˣ�ѡ��һ���뾧��ʱ�ӡ�����FPGA����ģ�鶼�õ������Ը���ģ�鶼��Ҫ����ͽӵء�

FPGA�ڲ���������������Խ��з�Ƶ�ͱ�Ƶ���Եõ���ͬ��Ƶ�ʡ���������FPGA�ṩģ��ת��оƬ�Ͳ�/��ת��оƬ��ʱ�Ӳ���ģ��ת��������İ�λ���ݱ����ʮλ���ݴ�������ת��оƬ�������8B10B��������ݴ��䡣��������FPGA�ṩ��ģת��������ʱ�Ӻʹ���ת�����IJο�ʱ�ӣ���������ת���������ʮλ���ݽ��룬��ԭΪ��λ���ݴ������ģת������FPGA�Ĺ�����Verilog���ʵ�֣��������AS(����)���÷�ʽ���ص�FPGA

2.3 ��Ƶ�źŵĴ������ɼ�

��Ƶ�źž��˲����Ŵ�ͬ�����룬��ģ��ת������оƬ�ɼ�ת���������źš�

2.3.1 �˲��Ŵ�

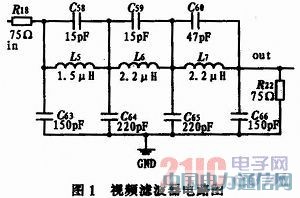

�ڶ���Ƶ�źŽ��в���ʱ�����ź��к��д��ڶ���֮һ�IJ���Ƶ�ʣ��������Ƶ�ʲ����ߣ��ͻ��������źš�����źŲ����������˲�������ȥ����Ҫ��Ӳ���˲���A/Dת���IJ���Ƶ����Ҫ������Ƶ�ź����Ƶ�ʵ�2��10����Ϊ����ģ��ת���β����ָ���Ƶ�ʣ��������ֻ�������źţ��˲�����A/Dת��֮ǰ���С�����������Ƶ�źŵĴ����Լ�������˲�����Ҫ�����ԣ����һ��7���ĵ�ͨ�˲�������ֹƵ��Ϊ6 MHz����·��ͼ1��ʾ��

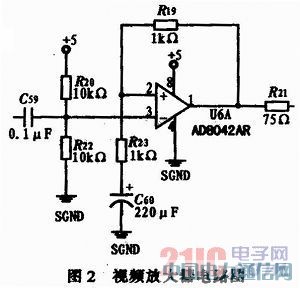

�Ŵ��·��������ģ��������˾��Ʒ�ļ���AD8042��ʵ�֡�AD8042��һ��ĵ͡���ѹ�����͵ĸ��ٷŴ����������е���Դ������������0.1BD����ƽ̹��Ϊ14 MHz������5 V��Դʱ�IJ���������λ���ֱ�Ϊ0.04����0.06����������5 V��Դʱ��������160 MHz�Ĵ�������ʧ��Ϳ��ٽ�������ʹ�����������ڻ��嵥��Դ������ģת����·����·��ͼ2��ʾ��

ͼ��AD8042����5 V��Դ���磬����һ���Ŵ�

2.3.2 ͬ�����벿��

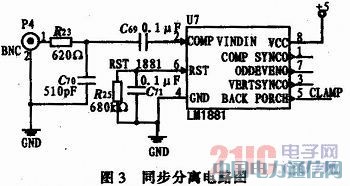

ȫ�����ź��г���ͼ���ź��⣬����������ͬ���źţ����С�����ɫ���ز�����ɣ���Щͬ���ź���ͼ�������źŰ���һ�����Ĺ�����ʽ���Ʊ����ɣ�ʹ��������Ƶ�ź�����Э��ͳһ�������ڽ��д��䴦����Ƶ�ź�ʱ��Ҫ�����е�ͬ���ź�ʵʩ�������룬�Ա���Ӧ���ƴ����������·����LM1881����оƬʵ�֡���оƬ�ɴ�ȫ�����ź�����ȡ���������кͳ�������ͬ������ż����ͼ����Ϣ��ͼ��ĸ�����Ƶ�ź�ֱ����ϵͳ������豸�ṩ��оƬ��BACK PORCH�ܽ�����Ƶ�ź������ڼ�����������壬�ýŽӵ�A/Dת����AD9280��CLAMP�˿ڼ�19�ţ�ʹA/Dת�������źŵ������ڼ䴦��ǯλ����ģʽ���ɽ�������ƽǯλ��0��ƽ��λ�ã��Ӷ�ʹ�òɼ������ź�ʱ�ܹ���ȷ�ð��ո����źż��ʱ���ϵ������ϵ�����ͬ���źŷ���Ĺ��ܡ�

�����·�����������Ұ뵼��������˾��Ʒ�ļ���LM1881��ʵ�֣���·��ͼ3��ʾ��

2.3.3 A/Dת������

ģ��ת����·ͬ����������ģ��������˾��Ʒ�ļ���AD9280��ʵ�֣��乤��ʱ��Ƶ���趨Ϊ32MHZ����FPGA�ṩ���ź���AIN�ܽ����룬D0��D7���ת�����8λ���������ݡ�STBY��THREE-STATE�Žӵأ��Ա�֤оƬ����������CLAPMIN�ӵأ���������ƽǯλΪ0��ƽ�����·��ͼ4��ʾ��

2.4 �źŷ��Ͳ���

��FPGA�����������Ҫͨ�����˷��ͣ������Ƚ���������ת��Ϊ�������ݣ��ٽ���������ת��Ϊ���źš�

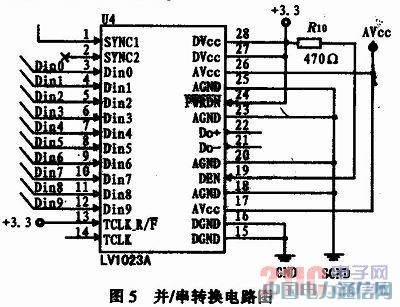

2.4.1 ��/��ת��

��·���ô�����DS92LV1023����оƬʵ�֣���·��ͼ5��ʾ�����Ӧ���ն��ɽ��DS92LV1224����оƬ��ɡ�DS92LV1023���Խ�10λ��������ת��Ϊ���в�����������ò��������������DS92LV1224��ԭΪ10λ�IJ������ݡ���һ��оƬ�ڲ������������Ϊ��������Լ�ƥ��ʱ�ӡ�������LV1023�ο�ʱ��ѡΪ32MHz�������ڸ�ʱ��Ƶ�������룬��оƬ�ڲ�ƥ������������ʱ�ӣ�ÿһ��10λ��������ת��Ϊ12λ�������ݣ����ж��һ����ʼλ��һ����ֹλ��������ЧƵ��Ϊ320 M������IJο�ʱ�Ӷ�Ϊ16MHz�����������ݴ�������

������Ƶ�ź���ʵʱ���ϵģ����������������������У����Ե�·�������ý������̬��ʡ��ģʽ�����LV1023��DEN��PWRDN���øߵ�λ��

�������ݵ�ȷ�������״������ͽ��ͬ��������оƬ��2��ͬ����ʽ��

1)����ͬ�� ������LV1023����һ��ͬ���źţ���������6��“1”��6��“0”��ɣ�����ͬ���ź�����SYNC1��SYNC2���Ƶģ���SYNC1��SYNC2�øߵ�ƽ����ʱ�䳬��6��ʱ������ʱ����ʼ��������ͬ���źţ������LV1224���յ�ͬ���źź�㿪ʼ��ͼ����ʱ���źţ��������֮ǰLOCK���ָߵ�ƽ��������ɺ�LOCK����Ϊ�͵�ƽ��

2)���ͬ����ʽ ����оƬ��û��ͬ���źŴ�����������Ȼ���������������ʹ����оƬ�ڿ��ų��ϵõ�Ӧ�á����ͬ��ʱ��������������ͬ���źţ����ֱ�ӶԲ��������������������������ʽ���ܵ���ʼʱ���ݺ�ʱ�ӵ���λӰ�죬Ҳ���ܵ����ݱ�����Ӱ�죬��һ�����������ͼ����������ʱ��������ܳ�����������ΪRMT������ͬ����ʧ�������������ʱ�ӣ��ָ�ͬ����

���ڸõ�·�������ͬ����ʽ����������SYNC1��SYNC2���ա�

2. 4. 2 ��/��ģ��

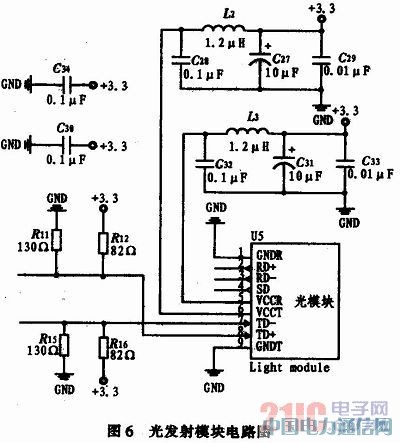

�����ͺ�ΪHNMS-XEMC41XSC20������������T1310nm/R1550nm�ĵ���˫��һ�廯�շ�ģ�飬�������Ų��������ת�ɹ������ź�������·��ͼ6��ʾ��

2.5 �źŵĽ��ռ�����

2.5.1 ��/��ת��ģ��

װ���Ե��˽����źŴ��䣬���źŴ��䵽����װ�ú���Ҫ��ԭΪ���źţ�����ֵ�ѹ�������������ͺ�ΪHNMS-XEMC41XSC20������������T1310 nm/R1550 nm�ĵ���˫��һ�廯�շ�ģ�飬�����ź�ת��Ϊ�����š�ת����IJ���ź���RD+��RD-�������·��ͼ7��ʾ��

2. 5. 2 ����ת��

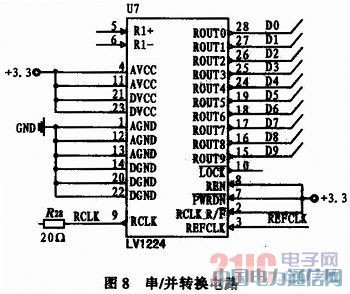

װ�ò����뷢�����еĴ�����DS92LV1023��ƥ��Ľ��DS92LV1224���������еĴ�������10λ�IJ�������ת��Ϊ���еIJ��������������ڽ�������������Ӧ�Ľ�������в����������ԭΪ�������ݡ�

DS92LV1224�ڲ���������ڽ���������ʱ���Ը������ݵ�Ƶ������ƥ�����ʱ�ӣ����ֻ��Ϊ���ṩ�ο�ʱ�ӡ��˴��ο�ʱ��ѡΪ16MHz����FPGA���Ʋ����ṩ��оƬ��ƥ�������������ͬ����ʱ�ӣ�������ת����IJ�������������ο�ʱ�Ӻ��������ʱ�ӷֱ�ΪREFCLK��RCLK���š�Ϊ�˱�֤��Ƶ�źŵ������Ժ�ʵʱ�ԣ������оƬ����ʡ��ģʽ�����ģʽ�����PWRDN��REN��Ӹߵ�ƽ��RCLK-R/F�Ӹߵ�ƽ����ѡ��ʱ��������������ݡ�

����оƬ��2��ͬ����ʽ������ͬ�������ͬ��������ͬ�����ɴ���������һ����������6��“1”��“0”��ɵ�ͬ���źţ�����յ��źź���������ʱ�ӣ��������֮ǰLOCK���ָߵ�ƽ��ͬ����ɺ�����Ϊ�͵�ƽ��ͬ���źŵķ������ɴ�������SYNC1��SYNC2���Ƶģ�ֻҪ����֮һ�øߵ�ƽ����ʱ�䳬��6��ʱ�����ڣ��������Ϳ�ʼ��������ͬ���źš�����ͬ�����п���ȷ���ŵ㣬���ڳ�������źŴ����У�����ֻ�������ݣ����ܺõĴ��ݴ������ͽ����SYNC��LOCK�źš���˲������ͬ����ʽ�����ͬ����ʽ���������跢��ͬ���źţ����ֱ�Ӷ�����������������ʵ��ͬ����������ʧ�������������ʱ�ӡ���LOCK�ӵ�FPGA�Խ���ʵʱ���ơ���/��ת����·��ͼ8��ʾ��

2.6 D/Aת������Ƶ�ź����

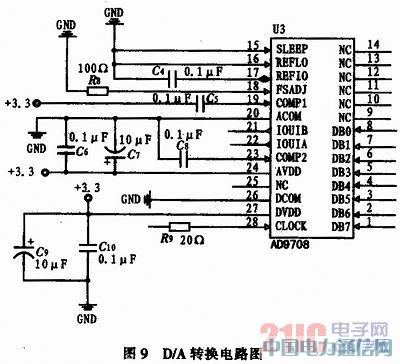

2.6.1 D/Aת������

��������ģ��������˾��Ʒ��AD9708�������ڸ����ܡ�����CMOS��ģת���������ṩ��ɫ�Ľ�����ֱ�����ܣ�֧�����125 Mz/s�ĸ������ʡ�����ʱ����Ϊ16 MHz����FPGA�ṩ��

AD9708����Χ��·��ͼ9��ʾ������REFLO��ת�����IJο��أ��˽Žӵؽ����ڲ��ο���ѹ��COMP1������˥��ģʽ���öˣ��˴�����0.1 μF�ĵ����ܴﵽ�Ϻõ�ת��Ч����R9���ն�ƥ�������������Ƶ��C9��C10�����˳����ֵ�Դ�Ʋ���C6��C7�����˳�ģ����Դ�Ʋ�������������DB0��DB7���룬ת�����������IOUTA������˴�������ź��뾭�˷ŷŴ��������ͨ������Ƶ��ʾ���ļ���Ҫ��

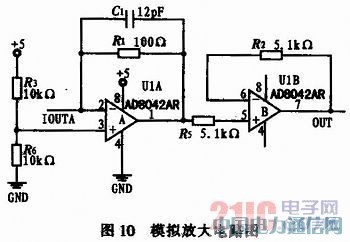

2.6.2 ģ��Ŵ���Ƶ�ź����

����AD8042ʵ���źŵķŴ���ͼ10��ʾ��ULA��AD9708����ĵ����ź�ת��Ϊ��ѹ�źţ�����C1��Ҫ������ȥ����Ƶ���š�ULB��Ϊ��ѹ�������������迹ƥ�䡣Ҫ�������迹��75 Ω����ѹ������ʹ����迹Ϊ0���ٴ���һ��75 Ω(��ULB��7��֮��ͼ��δ���)��������ƥ��Ҫ��

3 ������Ƽ�����

ϵͳ����VerilogHDL���Խ��г����д����Quartus���±༭���档FPGA�ڲ�ʱ����32 MHz�����ṩ��FPGA�Ĺ����ǣ�1)�ṩD/Aת��оƬAD9708��A/Dת��оƬAD9280������ת��оƬLV1023�Ĺ���ʱ�Ӻʹ���ת��оƬLV1224�IJο�ʱ�ӣ�����16 MHz��2)���Ͷ˶����ݽ���8B10B���룬����ת��������ݴ��������������ն˻�ȡ����ת�����ʮλ���ݣ����н��룬��ԭΪ����ǰ�İ�λ���ݣ��������������ݴ�����ģת��оƬ��

3.1 8B10B�����

8B10B������Ŀǰ���ٴ���ͨѶ�ձ���õı��뷽ʽ��8B10B�����Ŀ���ǽ���λ����ת����10λ�����ݣ���ʹת�������������“0”��“1”������ƽ�⣬���ⷢ������������ظ��ij���“0”��“1”�������Ĵ��������·��������ܣ������ڽ�������ȷ�IJ�ͬ��ʱ�ӣ����Ҳ����ض�����Ԫ����ʹ���ܶ˸�ȷ�ض���Ԫ��

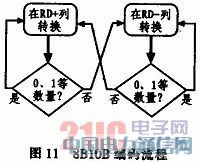

8B10B������Կ�����5B6B��3B4B�������ϣ���Ϲ�����Щ�������������ֵ��“1”��“0”�IJ�ֵ��Ϊƽ��ȣ���RD-��ʾƽ���Ϊ+2��0��RD+��ʾƽ���-2��0����ת��������ݽ�ƽ��ȷ�ΪRD-��RD+���С������DISPIN��ʾ����ת��������ƽ��ȣ�DISPOUT��ʾ��һ��ת��������ƽ��ȡ���ʼʱ��DISPIN��DISPOUT��ȣ��ȴ�RD-�п�ʼת�������ת�������“0”��“1”��������ȣ�������RD-����ת����һ���������“0”��“1”�������ȣ���ת��RD+����ת����ͬ����RD+���У����“0”��“1”��������������RD+�У�����RD-�С�

���벿�ֽ�10λ���ݵ�ǰ��λ�ͺ���λ�ֱ���5B6B��3B4B���б����뼴�ɡ�

3.2 ����

��Ƴ���Quartus���ۺ��������ۺϳɹ����Զ��������ݡ��м���������ݡ�������ݽ��з��档װ�ò��õ�8B10B���뷽ʽ����Ϊ3B4B��5B6B���б��롣���벿�����ձ���ʱ��ͬ�ķַ���ʮλ���ݷ�Ϊ4B��6B�ֱ���롣������ٰ�˳����ϳ�8λ���ݡ�������4B3B��6B5B�ֱ����ķ�ʽʵ�֡�

�������ͼ��ͼ12��ʾ��adin�DZ���֮ǰ�İ�λ���ݣ���Ϊ��μ�һ�ļ������ݣ�Ϊ�˷���Ƚϣ�ͼ����ʮ���Ʊ�ʾ��������ʮλ����Ϊdata10b��adout�ǽ��������ݡ����Կ��������ӳ٣������������Ϊ�������ݡ���˳������ȷ��ʵ�ֽ��빦�ܡ�

4 ������

ȫ�����ź��г�����Ƶ�ź��⣬��������Ƶ�źţ���������Ϣ�Ĵ�����ת����������Ӧ�������в���ȱ�ٵ��������걸�����˵���ͨ���⣬�շ��豸֮���������Ϣ������ʵ��˫��ͨ�š���ɷ�����ƹ��ܣ��ڹ���ͨ��Ӧ�������л�ù㷺Ӧ�ú��ռ�����Щ����ļ�������չ��ת������ֲ�����ʵ���ѧ��Ӧ���У�һ��������������ú����塣