ժҪ��ͨ���Գ��ÿ��ٸ���Ҷ�任�㷨ԭ�����о������������һ�ּ���Ч��FFT�㷨ʵ�ַ������÷����Ѿ���TMS320C64x DSP��ʵ�֡���FFT�㷨������CCS3.3�����У���֤�˸÷����Ŀ����ԡ���Ч�ԡ��÷�����Ӧ����LTE—TDD�����ۺϲ����DZ��Ŀ����С�

�������źŴ����У���ɢ����Ҷ�任(DFT)�dz��õı任���������ڸ��������źŴ���ϵͳ�а�������Ҫ�Ľ�ɫ�����ٸ���Ҷ�任(FFT)[1-2]����ɢ����Ҷ�任�Ŀ����㷨�����Ǹ�����ɢ����Ҷ�任���桢ż���顢ʵ�����ԣ�����ɢ����Ҷ�任���㷨���иĽ���õģ����߶���Ϊ�˽��źű任��Ƶ������Ӧ��Ƶ����������ʵʱ��Ҫ���ǿ���źŴ�����˵�������ٶȶ�����������Ӱ�����Զ����ġ���ΪFFTӵ�кܸߵ�����������ʹ��������ͨ�ź�����ͨ�š�����ͼ������ƥ���˲�������õ���Ϊ�㷺��Ӧ�á�

LTE��Ϊ4G������������Ƶ�ָ���OFDM�Ͷ���������MIMO����Ϊ���������в�������Ƶ�ֶ�ַ(OFDM)���������в��õ��ز�Ƶ�ֶ�ַ(SC-FDMA)��������20MHzƵ�״������ܹ��ṩ����100Mb/s������50Mb/s�ķ�ֵ����[3]��

Ƶ�������ʱ���������Խ�������������ڷ��������ź�[4]����LTEϵͳ�У�FFT�㷨��ҪӦ���ڻ����ź����ɡ��źŵĽ��պͼ��ȣ���ʱ���ź�ת�Ƶ�Ƶ����д�����

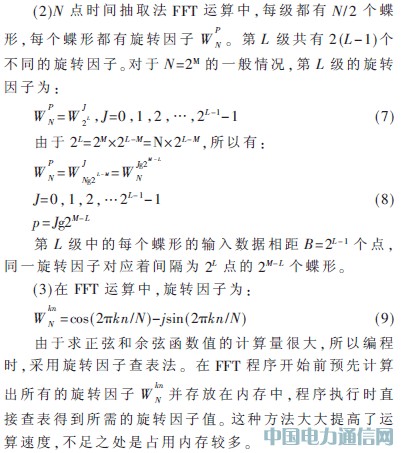

���У�x(n)Ϊ�������У�WNkn��X(K)ҲΪ���������ÿ����һ��X(K)ֵ����Ҫ����N�θ����˷������N-1�θ����ӷ����㡣��X(K)����N���㣬�����������DFT������Ҫ����N2�θ����˷���N(N-1)�θ����ӷ����㣬��N�ܴ�ʱ���������൱�ɹۡ�Ȼ������ʵʱ�Ժ�ǿ���źŴ�����˵����������Ҫ�������ٶȾ�̫���ˡ�������ת����WNkn�ĶԳ��ԡ������ԺͿ�Լ�ԣ�����ʹDFT�����е���Щ��ϲ����������е�DFT�ֽ�Ϊ���������е�DFT���Ӷ����������������FFT�㷨���Է�Ϊʱ���ȡ����Ƶ���ȡ�������ࡣƵ���ȡ���������ص���ʱ���ȡ���Ļ�����ͬ����֮ͬ����Ƶ���ȡ���ĵ����������ȼӺ�ˣ�ʱ���ȡ���ĵ����������ȳ˺�ӣ�Ƶ���ȡ��������������Ȼ˳����������ǵ���ʱ���ȡ�������������ǵ��������������Ȼ˳��

������������x(n)����ΪN=2M��M����������������������������������β����Ϊ�ؼ���������ֵ�㣬ʹ��ﵽ��һҪ������x(n)��n����ż�ֽ�Ϊ����N/2��������У�

2 FFT�㷨��DSPʵ��

2.1 Ӳ��

TMS320C6000ϵ��DSP��TI��˾�����г��ĸ�����DSP���ۺ���Ŀǰ�Լ۱ȸߡ����ĵ͵��ŵ㡣TMS320C64ϵ�������ʱ��Ƶ�ʣ�����ϵ�ṹ�ϲ�����VelociTI����ָ�VLIW(Very Long Instruction Word)�ṹ[5]��оƬ����8���������ܵ�Ԫ���ںˣ�ÿ�����ڿ��Բ���ִ��8��32bitָ�����ֵ�ٶ�Ϊ4800MIPS��2�鹲64��32bitͨ�üĴ�����32bitѰַ��Χ��֧��8/16/32/40 bit�����ݷ��ʣ�оƬ�ڼ��ɴ�����SRAM�����ɴ�8Mb�����ڳ�ɫ��������������Ч��ָ�����Χ��Ѱַ������ʹ���ر�����������վ�������DZ��ȶ����������ʹ洢��Ҫ��ߵ�Ӧ�ó��ϡ�

2.2 FFT�㷨��DSPʵ��

FFT�㷨��Ϊһ���Ӻ���ģ�����������г��Ȳ�����ͬ�����ԣ����������������������������ø�ʽ�����ø�ʽ��Turbo_Code(int*��int��int��char*��char*��int*)�����У�int�ֱ��ʾ�������еij��Ⱥ�FFT�ļ�����int*�ֱ��ʾ�������е���ַ��������е���ַ��char*�ֱ��ʾ��ת���ӵ����ҵ���ַ����ת���ӵ����ҵ���ַ��

FFT�㷨����ʵ���������£�

(1)ʱ���ȡ����FFT�У�ÿ�����ε����롢������ݽڵ���һ��ˮƽ���ϣ�����ÿ�����ε�������ݿ�����������ԭ����������ռ�õĴ洢��Ԫ������ԭλ����ɽ�ʡ�������ڴ棬���������ϼ��ٲ�ͬ�Ĵ���֮���ȡ���ݵ�ʱ�䡣

ʹ��C���Ա�д��������������Ա�дFFT�㷨��ʵ�ֺ����������м��������������Ϊ1024������DSP C6455����ֱ�Ӵ�ȡ����32bit���������ڴ��ж����˳���Ϊ8192bit��Ϊ���������е��ڴ�ռ䡣Ϊ��������㾫ȷ�ȣ���������ʵ�����鲿�ֱ�ռ��һ���֣��ڳ����н��и�����˲����Dz��û��ָ��MPYHI���ڴ涨���˳���Ϊ2048bit��Tempsequence��Ϊ��ŵ������У����ҽ�����2����ת���Ӳ��ұ����ֱ�ΪWr��Wi��

��ѭ���У���ÿ����ѭ��֮ǰ���������������ȡ��32bit����һ���Ĵ�������Ϊһ����ѭ�������룬��ѭ��������ȡ��һ��32bit������ظ�������Ĵ�����

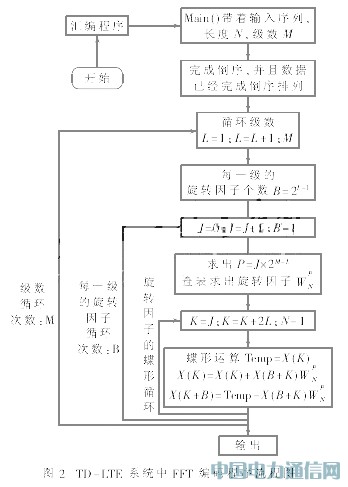

��ѭ���У�������ι��̲��ò���ķ�ʽ������ÿһ�����������Ҫ����ת���Ӹ����Լ���ͬ��ת�������ļ����������ι���ʱ��������ȡ��X(k)��������ͬ��ת���Ӽ���ҵ�X(k+B)��ɵ��μ��㡣���ǵ���ת���ӵĶԳ��ԣ����ڴ��д����ת����ʱֻ���һ�룬ʣ������ݸ��ݶԳ��Խ��д�����ͼ2������FFT�㷨ʵ�ּ�������ͼ��

��ʱ���ȡ����FFT���������ǵ��������������Ȼ˳��Ƶ�ʳ�ȡ����FFT������������Ȼ˳����������ǵ���ġ����ܲ������ַ�������FFT���㣬����Ҫ������������������FFT�������Ҫ���֣����л�����ʱ������Ȼ˳���������ݴ��뵽�洢��Ԫ�ڣ�ͨ����ַ���㣬����Ȼ˳������а�ʱ���ȡ��Ҫ����е�λ��

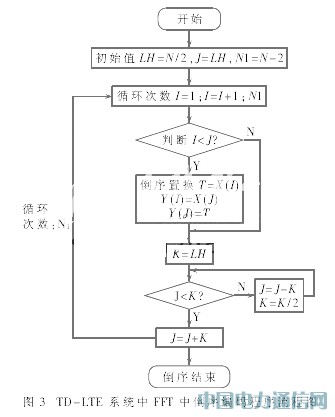

��������֮ǰ���洢��ԪY�����δ���������ݣ�I��ʾ��ǰ�������ݱ��ص�˳������ʮ������ֵ��I��ȡֵ��0��N-I��J��ʾ��ǰ��������ʮ������ֵ���������еĵ�һ�������һ������λ�ò���Ҫ����������ɵ������ѭ���Ĵ���ΪN-2��Ϊ�˱�֤�������ݵ���ȷ�ԣ���Ҫ���һ���Ƿ�I<J��ֻ�е�I<J���Ž�Y(I)��Y(J)�����ݻ������γɵ�����J�ԺͿ���ʵ�ֱ�ַ���ܣ�������Ȼ˳�����ڴ洢��Ԫ���������°��յ������С�ͼ3������ʵ�ֵ���Ļ������ͼ��

3 ���ܷ������ܽ�

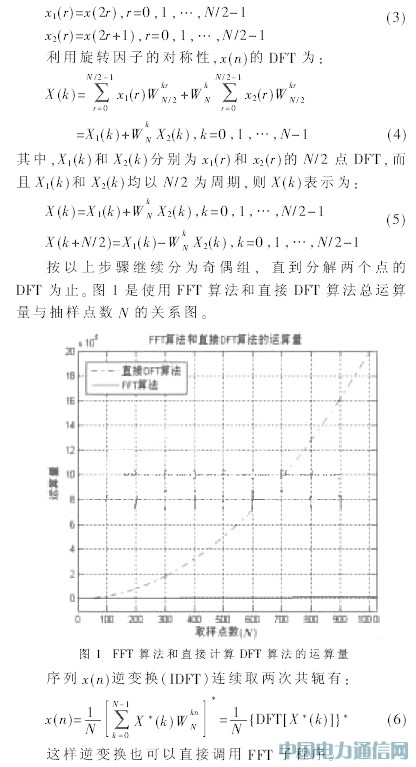

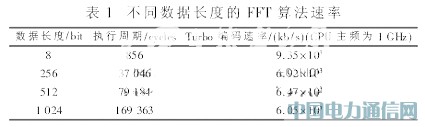

��DSP����ʵ���У�ͨ��ָ��У������Ż�����ѭ���壬���ٻ����������е�’NOP’ָ��[6]��ͨ������������У��õ�ͳ�ƽ�����1��ʾ��

�ӱ��п��Կ�����������TMS320C64×DSPоƬʵ��ʱ�����ڴ������ij�����Ƶһ��Ϊ1GHz��һ��ָ�����ں�ʱΪ1ns�����������ʷdz��죬��ȫ��������ʵʱ���źŴ�������ˣ�������ת���Ӳ������ʵ�ַ����������˳���ʵ�ַ�������������ģ���������д����Լ��ϵͳ�洢�ռ䡣

���������һ�ּ���Ч��FFT�㷨ʵ�ַ�������ϸ�������㷨��DSP��ʵ�ַ���������TMS320C64xоƬ�ϼ���ʵ�֡��������н�����������㷨�ܹ�����TD-LTEϵͳ�������п����Ժ�Ч�ԡ��÷�����Ӧ����LTE-TDD�����ۺϲ����DZ��Ŀ����С�

�����

[1] ������.�����źŴ���[M].�������������ӿƼ���ѧ�����磬2002.

[2] �η��ף��ŵ���.�����źŴ���[M].�������ߵȽ��������磬2009.

[3] 3GPP TS 36.211 v9.0.0.Evolved universal terrestrial radio access(E-UTRA) physical channels and modulation (Release 9)[S].2009-12.

[4] SAIDI A.Decimation-in-time-frequency FFT algorithm[M]. Manuscript��To be published.1993.

[5] Texas Instruments Incorporated.TMS320C64x/C64x+DSP CPU and instruction set referenceguide[EB/OL].Http://www.ti.com.cn��2008.

[6] Texas Instruments Incorporated.TMS320C6000ϵ��DSP��̹�����ָ��[M].�����������������������.�������廪��ѧ�����磬2006.