ժҪ�����GPS���������⣬�����ֶ������źŴ���ϵͳ�в�������Ӧ�����㷨��ʵ�ֿ����š���ϸ��㷨���и�����һ���źŴ���ϵͳ��Ӳ��ʵ�ַ��������ȸ���GPS����Ӧ�������ߵ�ϵͳ�ṹ��Ȼ������źŴ���ϵͳ��Ӳ�����˼·���书��ģ���ʵ�֣����ͨ��ʵ��������֤Ӳ��ģ�������������Ӧ�����㷨��Ҫ��

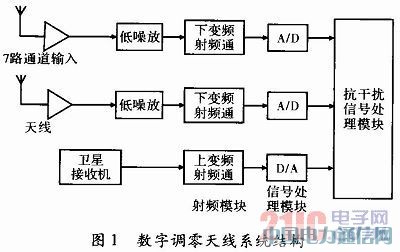

GPS��ȫ��λϵͳ(Global Positioning System)����һ���ɸ���ȫ���24��������ɵ�����ϵͳ����ϵͳ��ʵ�ֵ�������λ����ʱ�ȹ��ܡ���GPS�źűȽ������ܵз����ţ���֮���ƣ�δ���ҹ��ı����������ǵ���ϵͳҲ������ͬ�������⣬�����о�GPS������ϵͳ���ҹ����������ǵ���������չ������Ҫ��Ӧ�ü�ֵ�������Ŀ����ͱ�������Ͽ����ŵ����㷨���ȸ��������ֵ������ߵ�ϵͳ�ṹͼ��Ȼ����ϸ˵�����źŴ���ϵͳ������ģ��Ĺ�����ѡ�ͣ����ͨ������������֤���źŴ���ϵͳ��Ӳ�����������ĿҪ��

GPS������ϵͳ��������ֵ������ߣ����ź������ʽ��Ϊ��Ƶ�������Ƶ���������Ʒ��������ڵ�ǰ����Ͷ��ʹ�õ���ͨGPS���ǽ��ջ�δ����̭���ޣ�����û�п����Ź��ܡ����������Ƶ����Ŀ����ŵ������߷����������ڱ���ԭ�н��ջ��ṹ�����£����滻��Ƶ�˾Ϳ���ʵ�ֽ��ջ��Ŀ����Ź��ܣ����нϸߵľ���Ч�棻�����¿�����GPS���ջ���������ֵ�����Ƶ������������ַ����ṹ��ʵ���Ѷȵͣ������ȶ��ɿ�������GPS������ϵͳ�������ֵ���������Ƶ����ķ���������Ƶ����������ͨ������Ƶ���������ʵ�֡�

GPS���ֵ���������Ҫ������Ƶģ����źŴ���ģ�顣��Ƶģ�鸺���źŵķŴ��Ƶ��ת���Լ��ӿ�һ���ԣ���������Ƶͨ���а����ϱ�Ƶ��Ƶͨ�����±�Ƶ��Ƶͨ�����±�Ƶ�����ǰ������L1Ƶ���źű�Ƶ��14MHz��Ƶ�����ϱ�Ƶ�����ǰ���Ƶ�źű�Ƶ��L1Ƶ����ȥ���źŴ���ģ�鸺��ʵ�ֿ����ŵ����㷨�����ݴ��䡣

1 �źŴ���ϵͳӲ�������ʵ��

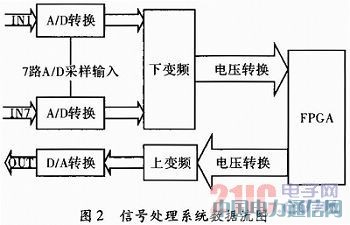

���źŴ���ϵͳӲ�����֮ǰ����Ҫ��ȷ�źŴ���ϵͳ����������������7·��Ƶģ���źŽ����źŴ���ϵͳ��ͨ��������ģ���ź�ת���������źţ�Ȼ���±�ƵоƬ����Ƶ�źű�Ϊ�����źţ���ƽת������FPGAʵ�ֿ����ŵ����㷨�������FPGA�����źž�����ƽת�����ϱ�Ƶ��ͨ����ģת�������Ƶģ���ź�����Ƶģ�顣

1.1 �źŴ�����ϵͳ

�źŴ��������źŴ���ϵͳ������Ҫ��оƬ����Կ����ŵ����㷨��������Ҫ����������ͬ�����ص㣬һ���������������������(1)ʹ�ö�Ƭͨ�ÿɱ��DSP��Ϊ�źŴ���оƬ��(2)ʹ�ø�����FPGA��Ϊ�źŴ���оƬ��ͨ�ö�ƬDSP�����������������������������㷨����ʵ�֣�����Ӳ��������û��̫�������ԡ���ƬDSPͬʱ�������ݣ�������ϵͳ���ȶ�������˸��ߵ�Ҫ�����źŴ�������7·�źţ�ÿһ·����16λ���ݺ�1λʱ�ӣ�������˶�Ĺܽ�Ҫ����ȻDSP������֮�����ӡ����ʹ��FPGA����������FPGA�зḻ��ͨ��I/O�ܽţ����������������ӣ�������FPGA��ʹ��״̬������ʵ��7·����ͬ���������㷨������ͬ����Ҫ�����ܵ�FPGA����ԭ�еĸ��ܶ����굥Ԫ������Ƕ��������ר��DSPӲ��ģ�飬���������㷨�Լ�������Ҫ��

�������Ҫ��Ϊ��֤7·����ͬ������Ҫʹ��FPGA��A/Dģ�顢���ֱ�Ƶģ�顢D/Aģ���ṩ��ͬ��ʱ���źţ������������Ĵ�����FPGAȫ��ʱ����Դ����������㷨��ͬһ��FPGA��ʵ�֣����п��ܲ���ʱ����Դ��ͻ����������źŴ�����ʹ������FPGA�ķ�ʽ����FPGA�ṩ�㷨��ʵ�֣���FPGA�������ṩʱ���źźͿ����źš����ַ�ʽ���ṩ���������ԣ����������ֻ�迼������FPGA���㷨������ģ������ı䡣

��FPGA�������ݵ�������־��һ��ϵͳ�����ܣ����ϵͳ����Xilinx��˾Virtex-6ϵ�е�XC6VLXT75T���������ṩ5616kB����Ƕ��RAM��ӵ�ж��288��DSP48E1������ͨ��I/O��360��������ʵ�ָ������˲��Լ����������źŴ������ܡ���FPGA��Ҫ�ṩʱ�ӺͿ����źţ�ϵͳѡ��Xilinx��˾Spartan-6ϵ�е�XC6Slx16���������ṩ2·CMT���Լ�576kB��RAM��232���û�I/O��

1.2 ���ֱ�Ƶģ��

���ֱ�Ƶһ�������ַ���ʵ�֣�һ����ʹ��FPGA����һ����ʹ��ר�ñ�ƵоƬ������FPGAʵ�ֱ�Ƶ�������������ص㣬�����ֱ�Ƶ��Ƽ������ϴ�ķѴ�����FPGA��Դ������������㷨Ҳʹ�ýϸ��ӵ��㷨�����п��ܲ�����Դ��ͻ�������ݴ������ʽϸ�ʱ��FPGAʵ�ֵ�����Զ����ר�����ֱ�Ƶ������

�����±�Ƶ�������ֽ������ͨ�˲��ȼ����������ڣ�����NCO��FIR�˲���������������±�Ƶ�������ϱ�Ƶǡ����֮�෴�����ڱ�ƵоƬ������·���ݣ�����ѡ��GC5016��Ϊר�����ֱ�Ƶ��������������TI��˾�Ƴ��Ŀ�Ƶ��4ͨ���Ŀɱ��������/�±�Ƶת�������ṩ150M sample·s-1ʱ�ӣ����нܳ���3G���ܡ����Ŀ��������˲����������������ӿ�ѡ���Լ������ġ�4����ȫ��ͬ�Ĵ���ͨ���ܶ������ó��ϱ�Ƶ���±�Ƶ�����������ϱ�Ƶ�������±�Ƶ��ϵ�ͨ������������ƶԱ�ƵоƬ��Ҫ��

1.3 A/Dģ��

A/D������ѡ��Ӧ�ñ�֤ϵͳ��ƹ��ܺ����ܵ�ʵ�֣���ҪӦ��4�����濼�ǣ�(1)A/D���ʵ�ѡ�����뵽A/D����Ƶ�ź�Ϊ16MHz������Nyquist����������ϵͳӦ�ø�A/D 32MHz�IJ������ʣ�����������������ʲ��������㷨�����������������㷨���������Ӧ��60MHz���ϡ�(2)���÷ֱ��ʽϸߵ�������A/D�����ķֱ�����Ҫȡ����������ת��λ�����������ź����뷶Χ���ɴ˿ɼ����ֱ���Խ��A/D����������Ⱦ�Խ�ߡ����ݼӸ���GPS�źŵĶ�̬��Χ�ϴ��ʵ���ص㣬��Ҫѡ��16λ�����ϵ�A/D������(3)���ݻ�������ѡ��A/Dת��оƬ�Ļ�������������Ŀ�Թ��IJ����У����Բ���Ϊѡ����Ҫ���ء�(4)���ݽӿ�����ѡ����ʵ�A/DоƬ���������±�Ƶ����������٣�������Ҫ���ݱ�Ƶ�����ӿ���ѡ��A/D��������֤A/D�����ܺͱ�Ƶ����ʵ�������ӡ�����Ҫ���ǵ�ƽ�ͱ��뷽ʽ�ȡ�

����4�����濼�ǣ��Լ��ο�A/D��˾���ϣ�����ѡ��AD9460��ΪA/Dת������AD9460����79dB������ȣ�������130Msample·s-1�ĸ�����Ƶ�������ʴﵽ16λ�ľ��ܶȣ�AD9460��80Msample·s-1�����ʹ���ʱ���书��Ϊ1.4W��

���ݿ����ŵ����㷨��Ҫ��7·��Ƶģ���źž���A/D��Ӧ��֤����ͬ����Ϊ��֤7·����ͬ����ʹ�ø�FPGA��7��A/D�ṩ��ͬ��ʱ���źţ���PCB�ϱ�֤��FPGA��7��A/DоƬ��ʱ����Ϊͬ����������������Ӳ���ϱ�֤����ͬ����

1.4 D/Aģ��

���ݾ����㷨����������������ϱ�Ƶ��ԭ����Ƶģ���źţ���Ҫѡ����֮����Ӧ��D/Aת��оƬ��ѡ��D/Aת��оƬʱ��Ҫ����3�������أ�(1)D/A��ת�����ȣ���ʵ����D/Aת�������ܵ���·Ԫ������������ѹ���Ⱥ�����Ŵ�������Ư������Ӱ�죬Ӧ���þ��Ƚϸߵ�D/Aת����оƬ��(2)�����ϱ�ƵоƬ������ݵı��뷽ʽ������λ���Լ����ʵȣ�ѡ��D/Aת����оƬ��֮�����ӣ���Ӧ����D/A�����̬�����Ƿ����������Ƶ�˵�Ҫ��(3)���ݻ�������ѡ��A/Dת��оƬ�Ļ���������

����ѡ��AD9747��ΪD/Aת��оƬ��AD9747�ǿ���̬��Χ��˫ͨ����ģת�������ֱ��ʴﵽ16bit����߲�������Ϊ250Msample·s-1����ת��������ֱ��ת������Ӧ�����ԣ����Ժ��������������������ӣ���־��D/A����ת�����ȵ�����������DNLֵΪ2LSB��INLֵΪ4LSB������ϵͳ��D/A������Ҫ��

2 �����źŴ���ϵͳ

�������źŴ���ϵͳӲ������ϸ��ƹ��̣�Ϊ��֤�źŴ���ģ��Ӳ���ܹ����������������������źŷ�������7·A/D����Ƶ��16MHz�����ֵ1V��ƫ��Ϊ0.5V�����Ҳ���7·���Ҳ�����A/D���������±�Ƶ����FPGAģ�飬��ʹ��Xilinx��˾�ṩ��ChipScope�۲�7·�źŵIJ��Ρ�ͼ3��ͼ4Ϊ������·ʹ��ChipScope��FPGA�й۲쵽�IJ��Ρ�

��ͼ��۲��֪����·�ź��ڷ�ֵ����λ�ϴ���һ�¡��ź�֮��IJ�ͬ�������ڵ�·�����������ɣ��粼�ߡ�оƬ֮��IJ���ȡ���Ϊ�㷨������ͬ�����ϸ�Ҫ�����Զ�����·�ź�������У����

������У������·�ź���ȫ�غϣ������㷨������ͬ����Ҫ��ͬ�������༸·�������ԣ�������·�����ͬ���Ӷ���֤�˴�A/Dģ�鵽FPGAģ����Ӳ�����������Ҫ����FPCA�а���һ·�ź�ֱͨ���ϱ�ƵоƬ��Ȼ����D/Aģ���������ʾ�����۲�ᷢ��һ��Ƶ��Ϊ16MHz�����Ҳ��������֤��FGPA��D/Aģ����Ӳ����Ҳ���������Ҫ��ġ�

3 ������

������������ֵ��������źŴ���ϵͳ��Ӳ����ƣ�ͨ��������֤��Ӳ������ȷ�ԣ����������ֵ��������㷨��Ҫ����һ��������(1)����Ƶ�˽��жԽӣ��������Ӳ��ϵͳ�ĵ��Թ�����(2)�����ֿ����ŵ����㷨��FPGA��ʵ�֡�