0 ����

CAN(Controller Area Network)����ISO�����һ�ִ���ͨ�����ߣ�����һ������Ч��֧�ָ߰�ȫ�ȼ��ķֲ�ʵʱ���Ƶ���һ������ͨ��Э�飬�����ֳ����߷��롣CAN���类�����Ϊ������������������ͨѶ���ڳ��ظ����ӿ���װ����ECU֮�佻����Ϣ���γ��������ӿ������磬ĿǰӦ�������Ѿ��൱�㷺��

��������֧��CANЭ���оƬ�����Ƴ�����CAN�����û������˼���ķ��㡣�����ҹ����ֳ���������������ӣ�CAN�����Ѿ����Ϊ�ҹ���õ��ֳ�����֮һ��

����CAN���ߵ�ECU���ӿ��Ƶ�Ԫ�Ŀ�����Ҳ�����������ŵ��о������ڶ�CAN����оƬ���о��Ѿ����پ����ڵ�һоƬ���о������ǰ����еĹ���оƬ��������һ��оƬ��ʵ��һ��������ECU�Ĺ��ܡ�

����ĿĿ��������FPGAʵ��һ��֧��CAN2��0Э������߿����������һ��ͨ�õ��ܹ�����CAN2��0Э���CAN���߿�������IP�ˣ������������Ժ��Ӧ���з���ļ��ɵ�����ϵͳ��ȥ������ʹ��VerilogHDL���ԣ������һ��֧��CAN2��0Э���CAN���߿�������������FPGAоƬ��CAN���������ж�������˲��ԣ�ʵ�������Ŀ�ġ����µ�ΪCAN_Registers����мĴ���ģ�顢λ�����������շ����ֹ��ܡ����Գ����ڸ�FPGA��CAN���߿������Ľڵ��·�ȡ�

1 CAN���߿��������

1��1 CAN�������������

1��1��1 �������

���ȶ�CAN2��0Э�����������ķ�����������CAN����Э��ĸ��������ݣ�������պͷ����˼��ֵ��͵�CAN���߿������Ĺ��ܣ����ѡ��PHILPS��˾������CAN���߿�����SJA1000���н�һ���ķ��������������ĸ�����ģ��Ĺ��ܡ�����Щ�����ϸ�����Ҫ�滮������Ƶ�CAN���߿������Ĺ��ܡ�

1��1��2 �������������֤

���������ɺ����ݹ��ܲ�����CAN����2��0Э�飬������������Ϊ���ɹ���ģ�飬��ȷ�˸�������ģ������á�ȷ��ģ�鼰�书��֮����Verilog HDL����ʵ���˸�ģ�����ơ����ţ�����Modelsim��������ƽ����˹�����֤��

1��1��3 ���ۺ�

���ܷ���ͨ���Ժ�����Quartus�������Ƶ�CAN���߿������������ۺϣ����������õ�FPGA�С�

1��1��4 Ӳ����֤

���õ�FPGA���Ժ�������ƵĻ���FPGA��CAN���߿�������Ϊһ���ڵ㣬�����SJA1000��Ϊ�������Ľڵ��·������ͨ�Ų��ԣ���֤������Ƶ�CAN���߿������Ĺ��ܡ�

1��2 CAN���߿��������������

1��2��1 ������SJA1000�Ĺ��ܽṹ

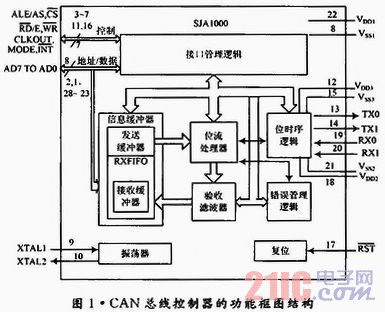

SJA1000��PHILIPS��˾��1997���Ƴ���һ�ֶ���CAN���߿�����������������һ�㻷���еĿ������������硣SJA1000��Ҫ�����¼������ֹ��ɣ��ӿڹ����������ͻ����������ջ������������˲�����λ��������������λʱ��������������ߡ�SJA1000��˫��ֱ��ʽ���ɵ�·�����ܿ�ͼ��ͼ1��ʾ��

1��2��2 �����п������Ĺ��ܽṹ

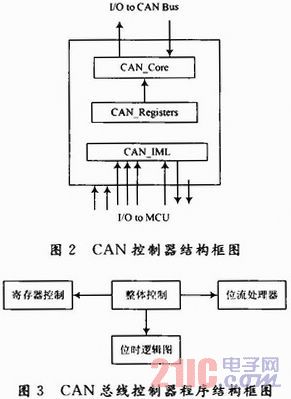

������Ƶ�CAN����������SJA1000�������Ľṹ�����ܻ�����ܰ�����ͼ2��ʾ��3������ģ�顣

CAN_IML��CAN���߿������ӿ�������Ҫ�����ǽ����������������������CAN�Ĵ�����Ѱַ�����������ṩ�ж���Ϣ��״̬��Ϣ��

CAN_CoreΪCANЭ��������ĺ��IJ��֣����CANЭ���е�������·���ȫ�������Լ�������IJ��ֹ��ܣ�����LLC�Ӳ�Ľ����˲�������֪ͨ�ͻָ�������MAC�Ӳ�����ݷ�װ����װ��֡���롢ý����ʹ����������⡢����궨��Ӧ��ʹ��л�����л����Լ��������λ���룯���롢λ��ʱ��ͬ����CAN_RegistersΪһ�Ĵ����飬�ⲿ����������ͨ����ֱַ�ӷ�����Щ�Ĵ��������ݹ��ܿ�ͼ�������CAN���߿������ij���ṹ����ͼ3��ʾ��

1��3 CAN���߸�������ģ������

1��3��1 CAN_IML���

����SJA1000�����FPGA CAN���߿������Ľӿڣ���ͼ4��ʾ��

ͼ��Port_0_io_7��Port_0_io_0Ϊ��ַ�����ݸ������ߡ�Cs_can_iΪƬѡ�����źš���Cs_can_iΪ0ʱ��������CAN���߿�������Ale_iΪ1ʱ�������ԼĴ������и�ֵ��Rd_i��Wr_iΪ�������Ķ�ʹ���źź�дʹ���źš�Irq_onΪ�ж�����źţ������ж���������Rst_iΪ��λ���룬���ڸ�λCAN�ӿڡ�Clkout_oΪFPGA CAN�������ṩ����������ʱ������źţ�ʱ�ӷ�Ƶ�Ĵ����ɽ�ֹ�����������Bus_off_on�������߹رպ����߿��Žӿڣ�Tx_o��Rx_i���շ��������������߷��ͺͽ������ݡ�

1��3��2 CAN_Registers���

��Ƶ�CAN���߿������ļĴ���ģ��������¼Ĵ�����ģʽ�Ĵ���������Ĵ�����״̬�Ĵ������жϼĴ������ж�ʹ�ܼĴ��������߶�ʱ�Ĵ���0��1���ٲö�ʧ����Ĵ�����������벶��Ĵ������������ƼĴ��������մ�������������ʹ�������������մ���Ĵ���0��3���������μĴ���0��3��������Ϣ�������ͽ��գ����ͻ�������

1��3��3 CAN_Core���

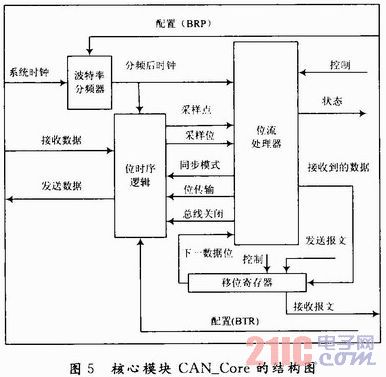

CAN_CoreΪ����CAN�������ĺ��ģ�������CAN��Э�顣����ģ����4��������ɣ��ṹ��ͼ5��ʾ��

�������CAN_Coreģ���е�λ����������λʱ������

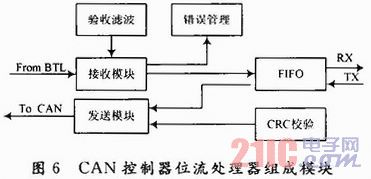

λ����������CAN���߿������п����������ķ�����������ִ�������ϵĴ����⡢�ٲá����ʹ������ȹ��ܡ���Ҫ�н���ģ�顢����ģ�顢�������ģ�顢CRCУ�顢�����˲���FIFO��6��ģ����ɣ���ͼ6��ʾ������CRCУ�顢FIFO�������˲�����ִ�е���Ŀ���Ѿ������������ɡ�

λʱ��������ư���λ��ʱ��ơ���������ơ�λͬ�����3���֡������Զ�λʱΪ����������ơ�

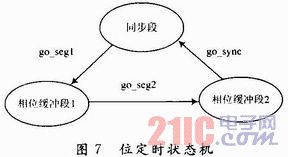

λ��ʱ��� ��λ��ʱ����в�����һ����3��״̬��״̬����3��״̬�ֱ��Ӧ����ͬ���κ���λ�����1�Լ���λ�����2��������ռ�õ�ʱ��̣��ڿ�����û���ر�����壬����Ϊ������Ĵ�����ʱ������û����ƽ�״̬����λ��ʱ���ֵ�״̬�������ͼ7��ʾ��

����ʹ��ModelSim����������Ƶĸ���ģ�������CAN���߿����������˹��ܷ��棬�����������ﵽ�����Ŀ�ꡣ

2 ������֤

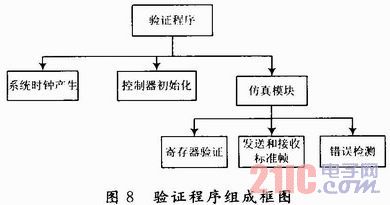

������������CAN���߿������IJ��Գ�����Ŀ����ģ��һ����������CAN���߿��������ж�д�������Ӷ�ʵ�ֶ�CAN���߿������ļĴ������ʣ���������շ����ܡ��ڸò��Գ����д�У��������ܻ��������������ʽʵ�֣����в�ͬ�ķ���ʱֻ�������ص�����ģ�顣ͼ8Ϊ��֤�������ɿ�ͼ��

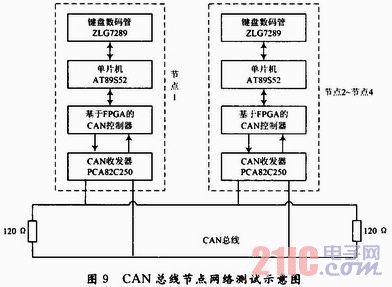

������֤����Ժ���HDL CAN���߳������ص�FPGA�н��в��ԣ�Ŀ��оƬ����Cycloneϵ�е�EP1C6Q240C8��Ϊ����֤����Ƶ�FPGA CAN���߿��������������һ����ڸ�FPGA��CAN���߿������Ľڵ��·��Ȼ����������ƵĽڵ��·������3������SJA1000��Ϊ��������CAN���߽ڵ������ͨ�Ų��ԡ����еĽڵ�ʹ��AT89S52��Ƭ����Ϊ�ڵ���������PCA82C250��Ϊ�շ��������Խ���������ص�FPGA�еĿ�����������������ʵ����Ԥ�Ƶ�CAN����ͨѶ���ܡ���������ʾ��ͼ��ͼ9��ʾ��

����ʱ�������ڵ�1�ϵĿ��ز�����״̬���͵��ڵ�2���ڽڵ�2������ʾ��Ӧ��״̬����֮Ҳ�ɡ�ͬʱҲ���ڽڵ�2ͨ����������ijһ���룬���ڽڵ�1�ϵ����������ʾ��Ӧ�Ľ������ʵ�����������ص�FPGA�еĿ�����������������

3 ����

����Ŀ����Verilog HDL���������һ��CAN���߿�����оƬ����ʹ��ModelSire����������Ƶ�CAN���߿����������˹��ܷ��棻֮��Ϊ����֤��ƣ�������һ����֤��������֤֮���������õ���FPGA�У����������ƵĻ���FPGA��CAN���߿�����������CAN�ڵ㣬������������SJA1000Ϊ��������CAN�ڵ������ͨѶ���ԣ�ʵ����CAN�������õĹ�������֤����Ƶ���ȷ�ԡ�