ЧЈ ТгЈ¬ЦЈ ұуЈ¬ФшБокҝЈ¬БхГчҝӯЈ¬ёЯ ІЁЈ¬СП Зҝ

ЈЁЦР№ъРЗНшНшВзУҰУГУРПЮ№«ЛҫЈ¬ЦШЗм 401120Ј©

0 ТэСФ

№эИҘөДТ»ДкЈ¬ОАРЗ»ҘБӘНшөД·ўХ№Из»рИзЭұЈ¬№ъНвјёёцРЗЧщПоДҝИЎөГБЛЦШҙуҪшХ№ЎЈStarlink јМРшА©ҙуЖдРЗЧщөД№жДЈЈ¬ФЪ№мөДОАРЗКэБҝТСҫӯі¬№э3 000 ҝЕЈ¬іэМṩПы·Сј¶·юОсНвЈ¬ЖдТөОсДЈКҪ»№А©Х№өҪәЈКВәНЖуТө·юОсЎЈҙЛНвЈ¬Oneweb РЗЧщОАРЗөДКэБҝТІҙпөҪБЛ462 ҝЕЈ¬ЖдФЪјёёц№ШјьКРіЎ¶јИЎөГБЛҪшХ№ЎЈЕ·ГЛУЪ2022 ДкРыІјБЛТ»По60 ТЪЕ·ФӘөДөН№мНЁРЕРЗЧщјЖ»®Ј¬¶шЦР№ъёьКЗНЁ№эБЛТ»ПөБР·ЁВЙЎў·Ё№жЦ§іЦГсУӘЖуТөҪЁФмөН№мНЁРЕОАРЗЎЈОАРЗЎўөзРЕ·юОсәНЦЗДЬКЦ»ъРРТө¶јіҜЧЕХэИ·өД·ҪПтВхіцБЛТ»ҙуІҪЎЈёьҫЯУРУ°ПмБҰөДКЗЈ¬Ж»№ы№«ЛҫФЪ2022 Дк9 ФВөДiPhone 14 ·ўІј»бЙПРыІјЈ¬ёГКЦ»ъҝЙУлGlobalstar ОАРЗБ¬ҪУЈ¬іхЖЪҝЙУГУЪҪфјұЗуҫИПыПўөД·ўЛНЎЈSpaceX әНT-mobileТІРыІјБЛОАРЗЦұҪУУлКЦіЦНЁРЕЙиұёөДәПЧчЎЈ»ӘОӘРыІјЖдMate50 ЦЗДЬКЦ»ъҪ«ДЬ№»К№УГЦР№ъұұ¶·ОАРЗөјәҪ·ўЛН¶МұЁОДЈ¬әуРшҪ«ҪшТ»ІҪЦ§іЦ¶МУпТфНЁ»°ЎЈХвР©БмУтЦРІ»¶ПіцПЦөДјјКхН»ЖЖФЪОАРЗТЖ¶ҜНЁРЕТөҪзПЖЖрБЛРВөДИИіұ[1]ЎЈ

ОАРЗТЖ¶ҜНЁРЕБмУтөДЧЁТөјјКх°ьә¬№г·әЈ¬Йжј°ОАРЗЎўФЛУӘТФј°ЦХ¶ЛөИёчёц»·ҪЪЎЈҙУНЁРЕЎўНшВзөҪЦХ¶ЛЙиұё¶јУРҫЮҙуөДСРҫҝҝХјдЎЈЖдЦРЈ¬ЦХ¶Л»щҙшҙҰАнЧчОӘОАРЗНЁРЕЦХ¶ЛөДәЛРДДЬБҰЈ¬ёьКЗіРФШЧЕОАРЗТЖ¶ҜНЁРЕ¶ЛІв·ўХ№өДЦШИОЈ¬КЗКөПЦОАРЗТЖ¶ҜНЁРЕЙМТө»Ҝ·ўХ№ұШРлН»ЖЖөДЦШТӘјјКх·ҪПтЎЈөұЗ°№ъНвөДОАРЗЦХ¶Л»щҙш№«ҝӘЧКБПҪПЙЩЈ¬ө«ҙУБгРЗөДұЁөАәНЖдЦХ¶ЛөДЙМТө»ҜіМ¶ИАҙҝҙЈ¬ЖдјјКхіЙКм¶ИТСҙпөҪҪПёЯЛ®ЖҪЎЈ°йЛжЧЕМмНЁОАРЗНЁРЕПөНіөД·ўХ№Ј¬№ъДЪөДОАРЗЦХ¶Л»щҙшТІ»эАЫБЛТ»¶ЁөДјјКхіЙ№ы[2]ЎЈө«КЗЛжЧЕОАРЗМеЦЖөД·ўХ№СЭҪшұд»ҜЈ¬ЦХ¶ЛГжБЩЧЕ¶аМеЦЖЎў¶аФШІЁөДёьёЯёьЗҝөДҙҰАнТӘЗуЈ¬ТтҙЛ¶ФЦХ¶Л»щҙшөДЙијЖТІҙшАҙБЛМфХҪЎЈ¶ФУЪ»щҙшҙҰАн¶шСФЈ¬ТӘҪвҫц¶аЦЦМеЦЖРЕәЕөДјжИЭРФҪУКХЈ¬ҫНұШРлТӘҫЯұёБй»оҝЙЕдЦГөДКэЧЦЗ°¶ЛЎЈКэЧЦЗ°¶ЛЧчОӘДЈДвУтУл»щҙшҙҰАнЦ®јдөДЗЕБәЈ¬КЗИнјюОЮПЯөзМеПөјЬ№№ПВ»щҙшҙҰАнІ»ҝЙ»тИұөДТ»Іҝ·ЦЎЈКэЧЦЗ°¶ЛөДЦчТӘИООсКЗёәФрКэДЈЧӘ»»әуөДІЙСщВКұд»»ЎўКэЧЦЙППВұдЖөЎўКэЧЦВЛІЁөИ№ҰДЬЎЈН¬Кұ»№ТӘҝјВЗІўРРФШІЁөДҫЫәП·ЦАлЈ¬ҫНұШРлТӘҫЯұёІўРРҙҰАнДЬБҰЎЈіэҙЛЦ®НвЈ¬»№ТӘјж№Л»щҙшҙҰАнЧКФҙ¶ФУЪ№ҰәДәНГж»эөДУ°ПмТтЛШЈ¬ХвҫН¶ФКэЧЦЗ°¶ЛХыМеөДЙијЖУРБЛёь¶аөДПёҪЪТӘЗуЈ¬ТтҙЛ¶ФЗ°¶ЛБҙВ·ЦРөДГҝТ»ёцДЈҝй¶јРиТӘҫ«РДҝјВЗЎЈ

1 »щҙшҙҰАнҪйЙЬ

»щҙшҙҰАнКЗХыёцТЖ¶ҜОАРЗНЁРЕЙПЧоәЛРДөДІҝ·ЦЈ¬ҝЙТФУГАҙ·ўЙдәПіЙТФәуөД»щҙшРЕәЕЈ¬»тХЯ¶ФҪУКХАҙЧФҝХҝЪөД»щҙшРЕәЕҪшРРҪвөчТлВлЎЈИзНј1 ЛщКҫЈ¬КэЧЦҪУКХ»ъ»щҙшҙҰАнТ»°г°ьә¬¶аёц№ҰДЬЧйіЙЈ¬ИзКэЧЦЗ°¶ЛЎўКұЖөН¬ІҪЎўҪвҪ»ЦҜЎўҪвИЕ/РЕөАұаТлВлөИ[3]ЎЈКэЧЦЗ°¶ЛФЪДЈКэЧӘ»»әуөДөЪТ»ІҪКЗНкіЙРЕәЕөДЧУФШІЁ·ЦАлЈ¬КЗұЈЦӨРЕәЕЦКБҝөД№Шјь»·ҪЪЈ¬Т»°гТФУІјюКөПЦЈ¬ИнјюКөПЦНщНщОЮ·ЁВъЧгКөКұРФөДТӘЗуЎЈКұЖөН¬ІҪРиТӘУГөҪРЕәЕ№АјЖөИКөПЦКұјдәНЖөВКөДҫАХэЈ¬ө«КЗЖдЛг·ЁёҙФУ¶ИёЯЗТұд»ҜҪП¶аЈ¬ТтҙЛНЁіЈИнУІјюҪбәПЎЈРЕөАұаТлВлТ»°гОӘНЁРЕЦРјЖЛгТӘЗуҪПёЯөДІҝ·ЦЈ¬ИзTurbo ТлВлЎўөНГЬ¶ИЖжЕјРЈСйВлЈЁLow Density Parity Check CodeЈ¬LDPCЈ©ТлВлЈ¬ЛщТФРиТӘТФУІјюөД·ҪКҪАҙМбёЯҙҰАнР§ВК[4]ЎЈЖдЛыөДҪ»ЦҜәНИЕВлөИјЖЛгҫщУРұкЧјөДёсКҪЈ¬ёҙФУ¶ИТІІ»ёЯЈ¬ЛщТФФЪКөјК№ӨіМЦРТІұИҪПИЭТЧКөПЦЎЈ

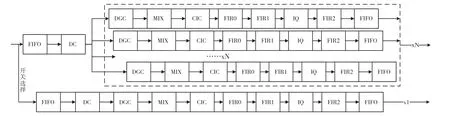

Нј1 »щҙшҙҰАн№эіМ

Хл¶ФөұЗ°ОАРЗТЖ¶ҜНЁРЕПөНіІ»Н¬МеЦЖөДјжИЭРФОКМвЈ¬Н¬КұОӘБЛНШХ№КХ·ўЙиұёөДНЁРЕіЎҫ°әННЁРЕДЬБҰЈ¬ФЪ»щҙшҙҰАнЙијЖКұЧціцБЛТ»¶ЁөДёДҪшЈ¬ТФұгОҙАҙККУҰ¶аДЈ¶аЦЖКҪөДУҰУГ[5]ЎЈәуОДҪ«ЦШөгІыКц»щҙшҙҰАнЦРКэЧЦЗ°¶ЛЈЁDigital Front-EndЈ¬DFEЈ©өДПкПёЙијЖәН·ВХжСРҫҝДЪИЭЎЈ

2 КэЧЦЗ°¶ЛЙијЖ

2.1 DFE КХ·ўБҙВ·ЧйіЙ

DFE ЧчОӘОАРЗЦХ¶Л»щҙшҙҰАнөДЦШТӘЧйіЙЦ®Т»Ј¬ҝЙТФМбёЯКэҫЭөДҙҰАнР§ВКЈ¬ҪөөНРЕәЕҙҰАнөДКұСУЎЈDFE ЦчТӘКөПЦВЛІЁЎў»мЖөЎўійИЎөИ№ҰДЬЈ¬ҙУ¶ш°СКэҫЭөДІЙСщВКҪөөНөҪҪПөНЛ®ЖҪЈ¬ТФұгҙҰАнәЛРДҪшРРИнјюҙҰАнЎЈТтҙЛЈ¬ФЪЙијЖКұЈ¬ТӘЧЫәПҝјВЗИлҝЪКэҫЭЛЩВКЎўПөНіҙшҝнЎўРЕәЕҙшҝнәНКөјКУҰУГөИТтЛШЎЈ

DFE °ьә¬ҪУКХәН·ўЛНБҪМхЦчТӘөДРЕәЕҙҰАнБҙВ·ЎЈЖдЦРҪУКХБҙВ·¶ФИлҝЪөДІЙСщКэҫЭҫӯ№эЦұБчҪГХэЎўКэЧЦПВұдЖөЎў»э·ЦКбЧҙЈЁCascaded Integrator-CombЈ¬CICЈ©ійИЎВЛІЁЎўәуј¶УРПЮіејӨПмУҰЈЁFinite Impulse ResponseЈ¬FIRЈ©КэЧЦВЛІЁЎўН¬ПаХэҪ»ЈЁIn-phase and Quadrature-phaseЈ¬IQЈ©ҪГХэЎўЖҘЕдВЛІЁөИҙҰАнұдОӘҪПөНІЙСщВКөДКэҫЭЎЈҪУКХБҙВ·ІЙУГЎ°N+1ЎұөДҪб№№Ј¬°ьАЁТ»В·өҘФШІЁәНА©ЖөёҙәПҙҰАн·ЦЦ§Ј¬БнНвNВ··ЦЦ§НкіЙ¶аВ·ФШІЁ·ЦАлөД№ҰДЬЎЈ·ўЛНБҙВ·УРіЙРНВЛІЁЎў¶юј¶ВЛІЁЎўCIC ДЪІеЎўЙП»мЖөЎўIQ РЈХэөИ№ҰДЬЈ¬·ўЛНБҙВ·РиТӘНкіЙ¶аВ·ФШІЁҫЫәПҙҰАнЈ¬»№РиТӘҫЯұёөҘФШІЁҙҰАнДЬБҰ[6]ЎЈDFE ЦРөДёчј¶ДЈҝй¶јҫЯУРҝЙұдЕдЦГІОКэЈ¬НЁ№эЧЬПЯНкіЙ¶ФУҰөДІОКэЕдЦГЈ¬КөПЦ¶ФУҰОпАнІгІЁРОөДКХ·ў№ҰДЬЎЈ

ИзНј2 ЛщКҫОӘ»щҙшҙҰАнөД¶аНЁөАDFE ҪУКХБҙВ·ЙијЖЈ¬НјЦР°ьә¬¶аНЁөАөДІҝ·ЦәНөҘНЁөАөДІҝ·ЦЈ¬ХвБҪЦЦІҝ·ЦҝЙТФЗР»»Ј¬НЁ№эјДҙжЖчЕдЦГІОКэСЎНЁЖдЦРТ»В·ЎЈ¶аНЁөАІҝ·ЦҝЙТФНкіЙ¶аёцЧУФШІЁөИІ»Н¬ЧйәПЗйҝцПВөДФШІЁ·ЦАлҙҰАнЈ¬ЖдЦРёчёцНЁөАөДІОКэҝЙТФөҘ¶АЕдЦГЈ¬ТІҝЙТФ№Ш¶ПЈ¬НЁөАЦ®јдЧйәП·ҪКҪБй»о¶аұдЈ¬ҙҰАнҪб№ыәН№эіМұЈіЦёЯ¶ИТ»ЦВРФЎЈөҘНЁөАІҝ·ЦҪцә¬ҙҰАнөҘёцФШІЁөДёчёцЧКФҙЧУДЈҝйЈ¬Хл¶ФөНЛЩөҘФШІЁәНёЯЛЩөДА©ЖөДЈКҪҪшРРБЛјжИЭРФҝјВЗЈ¬А©ҙуБЛІОКэЕдЦГәНҙҰАнДЬБҰ·¶О§ЎЈЛщУРҪУКХБҙВ·ЦРөДЧУДЈҝйҫщҫЯұёЕФВ·№ҰДЬЈ¬јҙЙиЦГПаУҰөДЕФВ·јДҙжЖчҫНҝЙТФК№РЕәЕКэҫЭІ»ҫӯ№эөұЗ°ЧУДЈҝйөДҙҰАнЈ¬ЦұНЁөҪПВТ»ј¶ЧУДЈҝйЎЈ

Нј2 DFE ҪУКХБҙВ·ЙијЖ

ИзНј3 ЛщКҫОӘ»щҙшҙҰАнөД¶аНЁөАDFE ·ўЛНБҙВ·ЙијЖҝтНјЎЈУлҪУКХБҙВ·АаЛЖЈ¬·ўЛНБҙВ·ТІ°ьә¬¶аНЁөАІҝ·ЦәНөҘНЁөАІҝ·ЦЈ¬І»Н¬ФЪУЪРЕәЕҙҰАнБчПтПа·ҙЎЈҪУКХКЗҙҰАнАҙЧФЙдЖөҪУҝЪөДКэҫЭЈ¬ІўҪ«КдіцНЁ№эЦұҪУҙжҙў·ГОКЈЁDirect Memory AccessЈ¬DMAЈ©°бТЖөҪДЪҙжЎЈ·ўЛНКЗНЁ№эDMA ·ҙПт°бТЖКэҫЭөҪДЈҝйҙҰАнЈ¬ЧоәуҙУЙдЖөҪУҝЪКдіцЎЈ·ўЛНБҙВ·өД¶аНЁөАКдіцЈ¬ЧоәуНЁ№эәПІўДЈҝйҪ«КэҫЭәПІўТФәуЛННщЙдЖөҪУҝЪЈ¬ёчёцНЁөАТІКЗ¶АБўІОКэЕдЦГәН¶АБў№ӨЧчЎЈөҘФШІЁНЁөАёьјУјт»ҜЈ¬КЎИҘБЛТ»ј¶ВЛІЁЈ¬УЕ»ҜБЛБҙВ·ЧКФҙПыәДЈ¬ІОКэТІҝЙТФБй»оЕдЦГЎЈ

Нј3 DFE ·ўЛНБҙВ·ЙијЖ

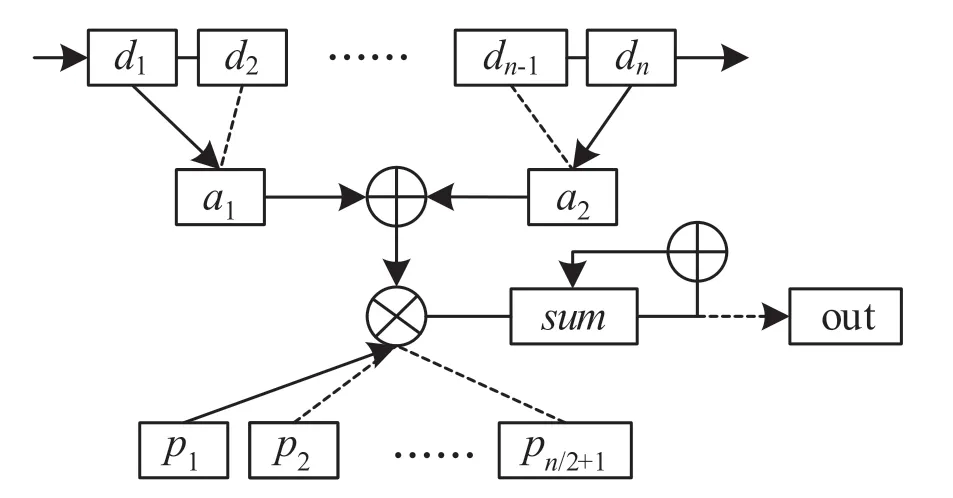

2.2 FIR ВЛІЁЖч

КэЧЦFIR ВЛІЁЖчұ»ҫӯіЈУГУЪЗ°¶ЛҙҰАнЈ¬УГУЪёДЙЖРЕәЕөДЦКБҝЎЈ¶ФУҰРЕәЕЛЩВКөДёДұдЈ¬ҪУКХРиТӘҪшРРійИЎВЛІЁЈ¬·ўЛНРиТӘҪшРРДЪІеВЛІЁЈ¬ійИЎәНДЪІеТтЧУөДЙиЦГ·¶О§ТӘЧг№»ёІёЗҝнХӯҙшІЁРОЎЈҙЛНвЈ¬НЁіЈФЪТ»ёцБҙВ·ЙијЖЦРРиТӘ·ЕИл¶ај¶ВЛІЁҪб№№Ј¬ВЛІЁЖчөДҪЧКэҝЙТФёщҫЭОпАнІгІЁРОЙијЖЈ¬ө«РиТӘҫЎҝЙДЬС№өНВЛІЁЖчҪЧКэЈ¬ҙУ¶шҪөөНЧКФҙПыәДЎЈҙ«НіөДFIRЦұҪУРНВЛІЁҪб№№ФЪјЖЛгКұЈ¬ЖдІОУлөДіЛ·ЁЖчәНјУ·ЁЖчёцКэУлВЛІЁЖчҪЧКэУР№ШЈ¬ҪЧКэФҪёЯПыәДөДіЛ·ЁәНјУ·ЁФҪ¶аЎЈФЪКөјК№ӨіМЦРЈ¬ОӘБЛҪөөНЧКФҙПыәДЈ¬ҝЙТФІЙИЎТ»Р©ЙијЖјјЗЙЈ¬АыУГёЯЛЩВККұЦУЈ¬ТФКұјд»»ИЎҝХјдөДЧц·ЁЈ¬ҪбәПСЎНЁЖчЈ¬АыУГөҘёціЛ·ЁәНјУ·ЁҫНҝЙТФКөПЦВЛІЁЖчөДНкХыФЛЛгЎЈИзНј4 ЛщКҫЈ¬dОӘҙ®РРКэҫЭБчЈ¬pОӘВЛІЁЖчПөКэЈ¬sumОӘЗуәНҪб№ыЎЈ·ЦұрСЎФсВЛІЁПөКэәНҙ®РРКэҫЭЈ¬ТАҙОҪшРРПајУПаіЛЈ¬іЛ·ЁҪб№ыФЩҪшРРАЫјУЗуәНЈ¬ЧоЦХКдіцТ»ёцВЛІЁҪб№ыЎЈИзҙЛҪб№№өДВЛІЁЖчПыәДөДЧКФҙҝЙТФҪөөНәЬ¶аЎЈ

Нј4 FIR ВЛІЁјт»ҜјЖЛгДЈРН

2.3 КэЧЦ»мЖөЖч

КэЧЦ»мЖөЖчТ»°гУГУЪЖөЖЧ°бТЖЈ¬ФЪРЕәЕҪУКХ№эіМЦРЈ¬Ҫ«өНЦРЖөөДКэЧЦРЕәЕұдөҪБгЖөЈ¬ФЪ·ўЛНөД№эіМЦРЈ¬°СБгЖөРЕәЕ°бөҪДҝұкЖөөгЙПЎЈТ»°гҙ«НіөДЧц·ЁКЗҪ«РЕәЕУлұҫөШФШІЁПаіЛЈ¬ХвСщҫНРиТӘІъЙъұҫөШФШІЁЈ¬І»ҪцРиТӘПыәДіЛ·ЁЖчЧКФҙЈ¬»№РиТӘХјУГҪПҙуҝХјдөДҙжҙўЧКФҙЎЈХвАпҪиЦъЧшұкКэЧЦРэЧӘјЖЛгЈЁCoordinate Rotation Digital ComputerЈ¬CORDICЈ©өДЛјПлЈ¬¶ФТӘ»мЖөөДГҝёцёҙРЕәЕІЙСщөгҪшРРРэЧӘЈ¬РэЧӘҪЗ¶И°ҙХХЖөВКҝШЦЖЧЦАЫјУЎЈЖөВКҝШЦЖЧЦөДјЖЛг·ҪКҪИзПВ[7]Јә

КҪЦРЈәf0ОӘ»мЖөДҝұкЖөВКЈ»fsОӘРЕәЕІЙСщВКЈ»NОӘЖөВК·ЦұжО»ҝнЈ»ҰӨОӘЖөВКҝШЦЖЧЦЎЈ

¶шФЪК№УГCORDIC Лг·ЁјЖЛгКұЈ¬ПаО»ҝШЦЖЧЦЛжЧЕІЙСщКэҫЭЦрөгјЖЛгІ»¶ПАЫјУЈ¬ФЪАЫјУ№эіМЦРЈ¬УЙУЪ¶Ёөг»ҜО»ҝнПЮЦЖЈ¬АЫјУЦөФЪТзіцәуЧФ¶ҜІ№іҘөҪРВөДПаО»ҝШЦЖЦөЈ¬И»әуГҝТ»ёцёҙРЕәЕөгҫН»бТФ¶ФУҰөДҰИ(n)ҪшРРРэЧӘЈ¬ЖдјЖЛ㹫КҪИзПВЈә

КҪЦРЈәҰИ(n)ОӘөЪnёцөгРиТӘРэЧӘПаО»Ј»ҰИ0ОӘіхКјПаО»Т»°гОӘ0Ј»Mod ОӘИЎДЈІЩЧчЎЈ

јЖЛгіцПаО»ТФәуЈ¬ҫНҝЙТФК№УГCORDIC өьҙъЛг·ЁҪ«КёБҝРэЧӘөҪДіёцҪЗ¶ИДҝұк[8]ЎЈДЗГҙРэЧӘҫШХуҝЙТФұнКҫОӘЈә

КҪЦРЈәRn(ҰИ)ОӘРэЧӘҫШХуЈ»ҰИnОӘРэЧӘПаО»ЎЈ

ОӘБЛұгУЪУІјюҙҰАнЈ¬НЁ№эТФПВИэҪЗәгөИКҪөИР§ЧӘ»»ЎЈ

НЁ№эПЮЦЖtan(ҰИn)=2-nЈ¬өұЖдОӘ2 өДГЭҙО·ҪәуЈ¬ФЪУІјюЙПҫНКЗјтөҘөДТЖО»ІЩЧчЎЈНЁ№эХвЦЦПЮЦЖЈ¬ФЪУІјюЙП»щұҫҫНІ»РиТӘИОәОЧКФҙөДҪб№№Ј¬Хв¶ФУЪ№ӨіМКөПЦАҙЛөКЗТ»ёцҫЮҙуөДУЕөгЎЈН¬КұУЙУЪУЦКЬПЮУЪРэЧӘҪЗ¶ИЈ¬ОӘБЛКөПЦИОТвҪЗ¶ИЈ¬ҫНІ»өГІ»КөПЦ¶аҙОРэЧӘөьҙъЈ¬ЧоЦХЗчҪьУЪДҝұкЦөЎЈРэЧӘ№эіМЦР»№ТӘЧўТвЗш·ЦКЗХэПт»№КЗДжПтөДРэЧӘЎЈХвСщөДІЩЧчёЕАЁОӘЈә

КҪЦРЈәxi-1Ј¬yi-1ОӘЗ°Т»ҙОРэЧӘәуөДёҙРЕәЕКөІҝәНРйІҝЈ»KiОӘФцТжТтЧУЈ»ҰТiОӘХэёә1 ҙъұнРэЧӘ·ҪПтЎЈ

ФЪДЈҝйҙҰАніхКјКұРиТӘ¶ФФцТжТтЧУҪшРРІ№іҘЈ¬өьҙъ¶аҙОФцТжЗчҪьУЪТ»ёцОИ¶ЁЦөЎЈДЗГҙІ№іҘЦөОӘёГҪьЛЖЗчҪьЦө[9]ЎЈЗуј«ПЮИзПВКҪЈә

Т»°г№ӨіМЙПЈ¬ТӘҙпөҪҪПәГөДҫ«¶ИТӘЗуЈ¬НЁіЈТӘЗуөьҙъ14 ҙОТФЙПЎЈ»мЖөЖчөДКдИлРЕәЕ·щ¶ИТІРиТӘҝШЦЖФЪҪПәГөДПЯРФ·¶О§ДЪЈ¬РЕәЕМ«РЎФтБҝ»ҜОуІо ҪПҙуЎЈ

2.4 »э·ЦКбЧҙПЯВЛІЁЖч

CIC ВЛІЁЖчТСҫӯУҰУГҪП¶аЈ¬Т»°гФЪРЕәЕҙшҝнұИҪПҝнЎўІЙСщійИЎ»тДЪІеұ¶КэұИҪПёЯөДКұәтЈ¬FIR ВЛІЁЖчөДК№УГРФјЫұИҫНІ»КЗМШұрёЯБЛЈ¬ЛщТФСЎУГCICАҙКөПЦёЯұ¶КэөДІЙСщВКұд»»ҝЙТФУРР§ҪөөНЧКФҙЈ¬јхРЎөзВ·Гж»эЎЈ

¶ФУЪCIC ВЛІЁЖчөДЙијЖЈ¬ЦчТӘ№ШЧўійИЎәНДЪІеТтЧУЎўВЛІЁј¶БӘКэЎўСУКұТтЧУХвјёёцЦёұкЎЈУЙ»э·ЦЖчәНІо·ЦЖчј¶БӘөДҙ«өЭәҜКэ[10]ұнКҫОӘЈә

КҪЦРЈәNОӘВЛІЁЖчј¶БӘҪЧКэЈ»DОӘійИЎТтЧУЈ»MОӘСУКұТтЧУЈ¬Т»°гОӘ1 »т2Ј¬НЁіЈСЎ1ЎЈ

ЛжЧЕCIC ј¶КэөДФцјУЈ¬ЖдЧиҙшЛҘјхТІ»бФцјУЈ¬ҙшДЪЛҘјхТІ°йЛжЧЕФцјУЎЈТтҙЛЈ¬ФЪ¶ај¶ј¶БӘКұЈ¬ОӘБЛ»сөГБјәГөДНЁҙшЖҪМ№МШРФЈ¬Т»°гЙијЖCIC ВЛІЁЖчөДј¶КэІ»і¬№э5 ј¶ЎЈБнНвЈ¬ҝјВЗөҪКөјКК№УГЙПөДБй»оРФЈ¬CIC ВЛІЁЖчөДј¶КэОӘ4 ј¶»т5 ј¶ҝЙСЎФсЎЈійИЎәНДЪІеТтЧУТІЙијЖОӘ1Ў«256 ҝЙЕдЦГЎЈ

ФЪCIC өДјЖЛг№эіМЦРЈ¬»бІъЙъО»ҝнА©Х№Ј¬К№КдИлРЕәЕУРФцТжЎЈО»ҝнА©Х№јЖЛгИзПВЈә

КҪЦРЈәBinОӘКдИлКэҫЭО»ҝнЈ»BoutОӘКдіцКэҫЭО»ҝнЈ»ОӘПтЙПИЎХыЎЈ

CIC өДЦРјд№эіМОӘБЛККУҰИ«¶ҜМ¬·¶О§Ј¬РиТӘұЈіЦЧоҙуА©Х№О»ҝнҫ«¶ИјЖЛгЈ¬ФЪКдіцҪб№ыКұёщҫЭійИЎ»тДЪІеТтЧУҪШО»ЎЈАэИзО»ҝн[B:0]ҪШИЎnО»Ј¬ДЗГҙКдіц[B:n]+[n-1]ЧчОӘЧоЦХКдіцҪб№ыЈ¬ХвСщөДҪШО»·ҪКҪУлЛДЙбОеИлnearest()әҜКэөИР§ЎЈ

2.5 ФцТжҝШЦЖДЈҝй

КэЧЦФцТжҝШЦЖЈЁDigital Gain ControlЈ¬DGCЈ©КЗұЈЦӨКэЧЦЗ°¶ЛРЕәЕКХ·ў·щ¶ИҝЙҝШөД№ШјьДЈҝйЎЈК№өГРЕәЕДЬ№»°ҙХХФӨ¶Ё·щ¶ИТӘЗу·ўЛНЦБМмПЯЈ¬ҪУКХРЕәЕФЪ»щҙшҙпөҪФӨ¶Ё·¶О§ұгУЪәуј¶ФЛЛгҙҰАнЎЈХвАпІЙУГҝӘ»··ҪКҪЈ¬УЙЧЬПЯЕдЦГјДҙжЖчФцТжЦөәНҪШО»ІОКэЈ¬НЁ№эіЛ·ЁәНТЖО»јЖЛгТФҙпөҪДҝұкФцТжҫ«¶ИөДТӘЗуЎЈҫЯМејЖЛ㹫КҪИзПВЈә

КҪЦРЈәx(n)ОӘКдИлРЕәЕЈ»y(n)ОӘКдіцРЕәЕЈ»GОӘФцТж ЦөЈ»AОӘјДҙжЖчЕдЦГФцТжІОКэЈ»iОӘТЖО»О»КэЎЈ

ФЪКөјКјЖЛг№эіМЦРЈ¬ІОКэЕдЦГөДФцТжЦөЦ»»бҪьЛЖДҝұкФцТжЦөЈ¬ФЪ№ӨіМЙПҙпөҪҝЙҪУКЬөДОуІо·¶О§ јҙҝЙЎЈ

2.6 IQ ҪГХэДЈҝй

ФЪКөјКУҰУГ№эіМЦРЈ¬УЙУЪКЬЖчјю№ӨТХөДПЮЦЖЈ¬ФЪН¬ПаЦ§В·әНХэҪ»Ц§В·ЙПөДВЛІЁЖчЎў»мЖөЖчөИДЈДвЖчјюОЮ·ЁұЈЦӨТ»ЦВРФЎЈҪш¶шөјЦВI В·әНQ В·РЕәЕПаУҰҙжФЪТ»¶ЁөДІоТмЈ¬ЦчТӘұнПЦОӘҫөПсЖөЖЧ·ЦБҝЎўРЗЧщөгК§әвЎўРЕәЕСПЦШК§ХжЈ¬К№ХыёцНЁРЕПөНіөД¶ҜМ¬·¶О§әНБйГф¶ИПВҪөЎЈ

ОӘБЛҪвҫцЙПКцОКМвЈ¬ЧЁГЕЙијЖБЛIQ ҪГХэДЈҝйЈ¬НЁ№эЕдЦГҪГХэТтЧУАҙҫАХэIQ І»ЖҪәвөДОКМвЎЈКЧПИМбЗ°№АјЖіц·щ¶ИәНПаО»І»ЖҪәвІОКэ[11]Јә

КҪЦРЈәyI(n)Ј¬yQ(n)ОӘН¬ПаәНХэҪ»·ЦВ·өДІЙСщРЕәЕЈ»ҰБОӘ·щ¶ИҪГХэТтЧУЈ»ҰХОӘПаО»ҪГХэТтЧУЎЈ

ЙПКцҪГХэТтЧУФЪМбЗ°№АЛгіцТФәуЈ¬НЁ№эјДҙжЖчөД·ҪКҪРҙИлЕдЦГІОКэЎЈОӘБЛјхЙЩФЪУІјюЙПКөПЦИэҪЗәҜКэөДФЛЛгЈ¬ҝЙТФ¶ФҪГХэТтЧУјЖЛгТФәуХыМеЕдЦГіЛ·ЁПоЎЈ

2.7 ЦұБчҪГХэДЈҝй

УЙУЪЖчјю№ӨТХЎўұҫХсР№В¶ЎўМмПЯЎўОВ¶ИөИ¶аЦЦТтЛШ¶ј»бөјЦВБгЦРЖөҪУКХ»ъІъЙъЦұБчЖ«ЦГЈ¬ЛщТФФЪҪУКХҙҰАнЦ§В·ЙПРиТӘҪшРРЦұБчҪГХэЎЈ№ӨіМКөПЦКұЈ¬АыУГРЕәЕөДНіјЖМШРФ¶ФЖдЦұБчЖ«ЦГЦөҪшРР№АјЖЈ¬IЎўQ БҪВ·өДЦұБчЖ«ЦГ№АјЖЦө[12]ОӘЈә

ФЪөГөҪЦұБч№АјЖЦөТФәуЈ¬НЁ№эҪГХэ№«КҪҝЫјхЦұБч·ЦБҝЎЈФЪКөјК№ӨіМЦРЈ¬ҝЙТФМбЗ°ёщҫЭөзВ·Жф¶Ҝ№АјЖБчіМЈ¬ІЙСщөЧФлЧчОӘСщұҫЈ¬И»әу°СМбЗ°№АјЖЦөҙжҙўФЪјДҙжЖчАпЈ¬ЧчОӘәуРшҝХҝЪКХ·ўөДҪГХэЦөЎЈТІҝЙТФУГИнјюҝШЦЖКөКұҪГХэЎЈ

КҪЦРЈәIDC(n)Ј¬QDC(n)ОӘҪГХэТФәуөДН¬ПаәНХэҪ»Ц§В·ІЙСщРЕәЕЎЈ

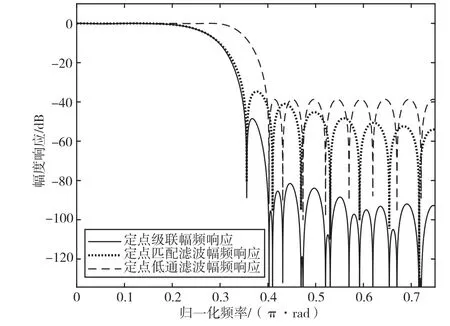

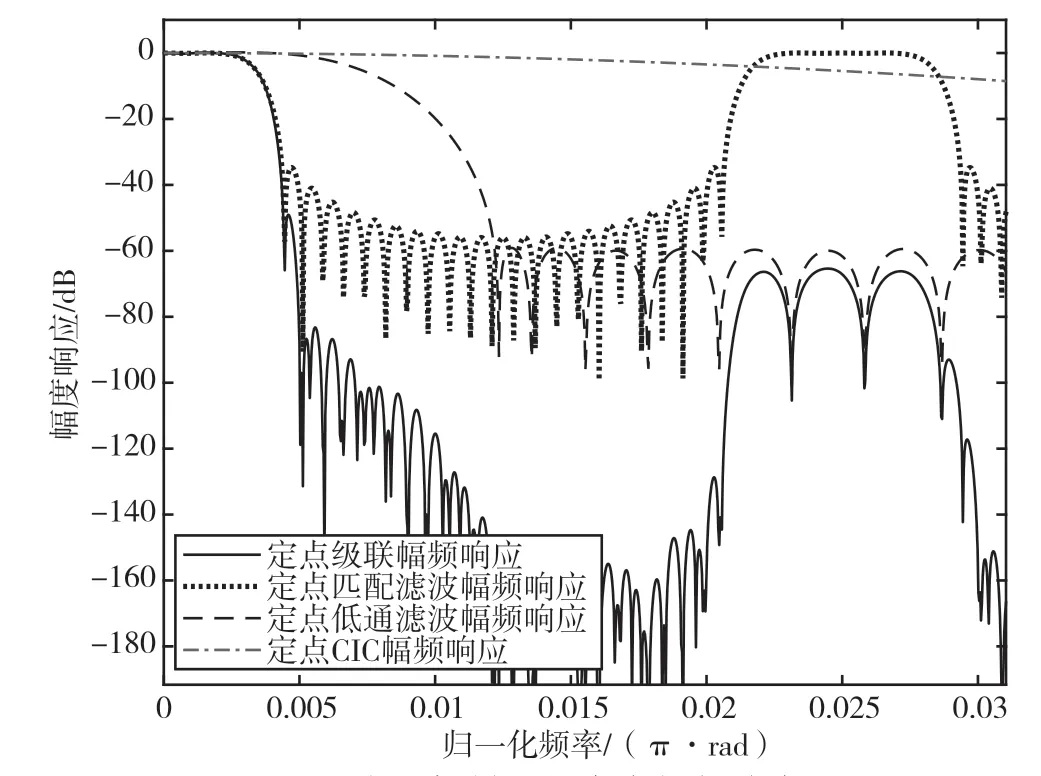

3 БҙВ·ІОКэ·ВХж

»щУЪЗ°КцөДDFE КХ·ўБҙВ·ЙијЖЈ¬ЕдЦГІ»Н¬ФШІЁіЎҫ°ҪшРРБҙВ·ІОКэ·ВХжЈ¬°ьә¬КХ·ўНЁөАөД·щЖөПмУҰТФј°КХ·ўРЕәЕөДОуІоПтБҝ·щ¶ИЈЁError Vector MagnitudeЈ¬EVMЈ©ЖА№АЎЈ

3.1 ·ўЛНБҙВ··ВХж

ЕдЦГіЎҫ°1ЈәөҘФШІЁ·ўЙдНЁөАЈ¬КдИл·ыәЕЛЩВКRd1Ј¬КдіцРЕәЕІЙСщВКfs1Ј¬ВъЧгfs1=4Rd1№ШПөЎЈ

ЕдЦГіЎҫ°2Јә¶аФШІЁ·ўЙдНЁөАЈ¬КдИл·ыәЕЛЩВКRd2Ј¬КдіцРЕәЕІЙСщВКfs2Ј¬ВъЧгfs2=256Rd2№ШПөЎЈ

ЕдЦГіЎҫ°3Јә¶аФШІЁ·ўЙдНЁөАЈ¬КдИл·ыәЕЛЩВКRd3Ј¬КдіцРЕәЕІЙСщВКfs3Ј¬ВъЧгfs3=1 280Rd3№ШПөЎЈ

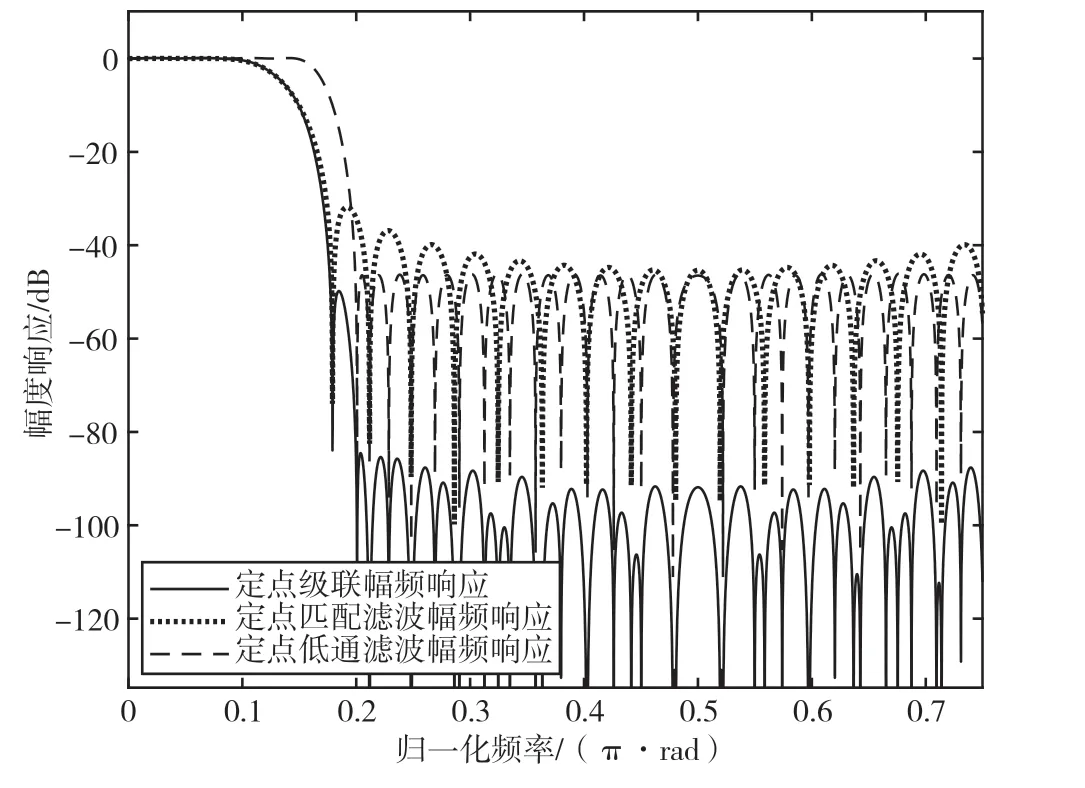

ТФЙП·ВХжіЎҫ°·ЦұрИзНј5ЎўНј6ЎўНј7 ЛщКҫЈ¬ұнКҫІ»Н¬·ўЛНіЎҫ°ПВөДНЁөА·щЖөПмУҰЈ¬ҝЙТФ·ўПЦНЁөАөДНЁҙшәНЧиҙшЦёұк¶јұИҪПУЕЈ¬¶ЁөгЛг·ЁөДРФДЬУлёЎөгҪУҪьЈ¬НкИ«ҝЙТФУІјюКөПЦЎЈ

Нј5 ·ўЛНіЎҫ°1 өД¶Ёөг·щЖөПмУҰ

Нј6 ·ўЛНіЎҫ°2 өД¶Ёөг·щЖөПмУҰ

Нј7 ·ўЛНіЎҫ°3 өД¶Ёөг·щЖөПмУҰ

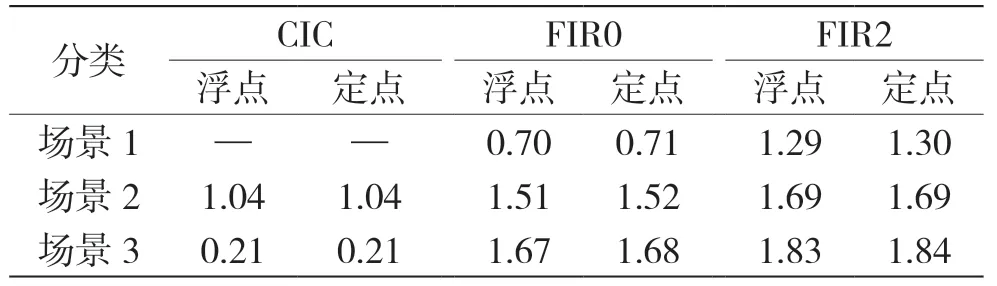

ФЩ¶ФұИ·ўЛННЁөАІ»Н¬іЎҫ°ПВөДEVMЈ¬РЕәЕөчЦЖ·ҪКҪІЙУГХэҪ»ПаТЖјьҝШЈЁQuadrature Phase Shift KeyingЈ¬QPSKЈ©Ј¬БҙВ·ЦРҪЪөг·ВХжҪб№ыИзұн1 ЛщКҫЎЈ

ұн1 ·ўЛНБҙВ·EVM ·ВХжҪб№ы/%

ҙУұн1 ҝЙТФҝҙіцЈ¬¶ЁөгЛг·ЁБҙВ·өДEVM РФДЬҪУҪьёЎөгЈ¬ОуІоФЪ0.01 ЧуУТЎЈ

3.2 ҪУКХБҙВ··ВХж

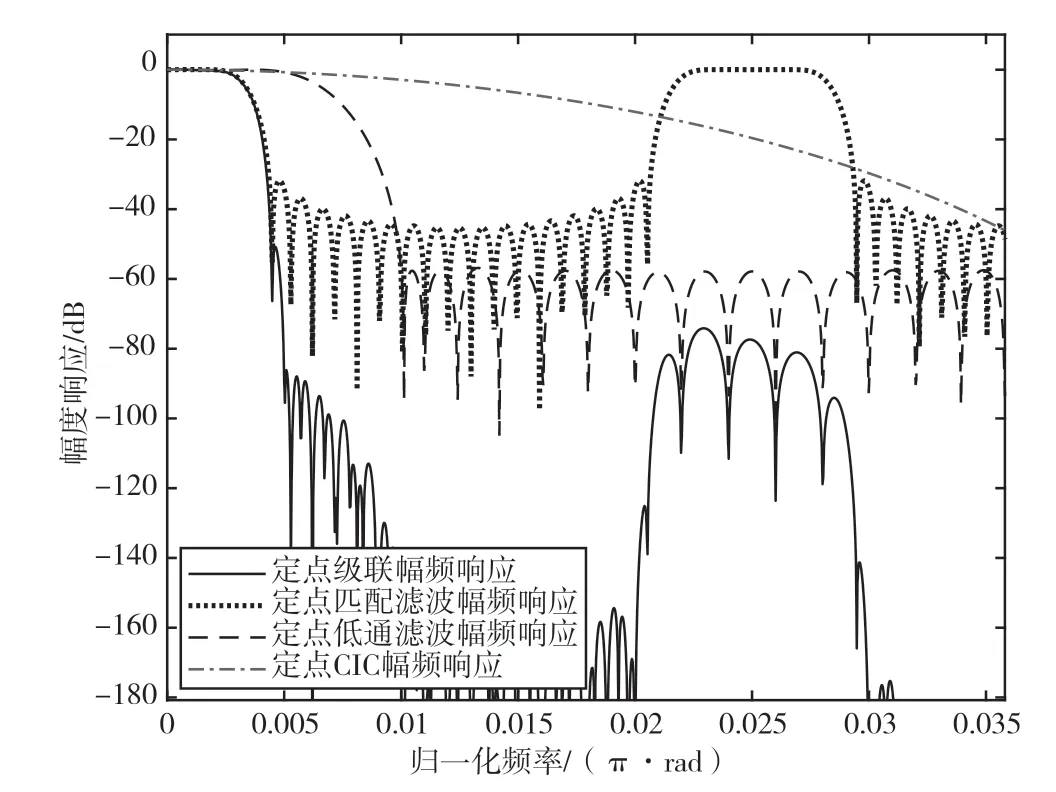

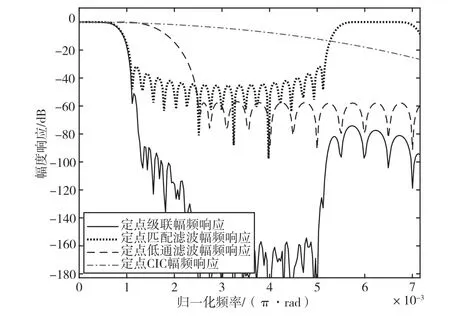

Н¬СщХл¶ФҪУКХНЁөАТІЧцБЛН¬АаіЎҫ°өД·ВХжЎЈИзНј8ЎўНј9ЎўНј10 ЛщКҫЈ¬·ЦұрОӘТФПВ3 ЦЦіЎҫ°өД·щЖөПмУҰЎЈЖдРФДЬУлёЎөгТ»ЦВЈ¬ПмУҰМШРФЗъПЯөДРФДЬ ҪПәГЎЈ

Нј8 ҪУКХіЎҫ°1 өД¶Ёөг·щЖөПмУҰ

Нј9 ҪУКХіЎҫ°2 өД¶Ёөг·щЖөПмУҰ

Нј10 ҪУКХіЎҫ°3 өД¶Ёөг·щЖөПмУҰ

ЕдЦГіЎҫ°1ЈәөҘФШІЁҪУКХНЁөАЈ¬Кдіц·ыәЕЛЩВКRd1Ј¬КдИлРЕәЕІЙСщВКfs1Ј¬ВъЧгfs1=4Rd1№ШПөЎЈ

ЕдЦГіЎҫ°2Јә¶аФШІЁҪУКХНЁөАЈ¬Кдіц·ыәЕЛЩВКRd2Ј¬КдИлРЕәЕІЙСщВКfs2Ј¬ВъЧгfs2=256Rd2№ШПөЎЈ

ЕдЦГіЎҫ°3Јә¶аФШІЁҪУКХНЁөАЈ¬Кдіц·ыәЕЛЩВКRd3Ј¬КдИлРЕәЕІЙСщВКfs3Ј¬ВъЧгfs3=1 280Rd3№ШПөЎЈ

ҪУКХНЁөАІ»Н¬іЎҫ°ПВөДEVMЈ¬РЕәЕөчЦЖ·ҪКҪІЙУГХэҪ»ПаТЖјьҝШQPSKЈ¬·ВХжҪб№ыИзұн2 ЛщКҫЎЈ

ұн2 ҪУКХБҙВ·EVM ·ВХжҪб№ы/%

4 ҪбУп

ёщҫЭОАРЗТЖ¶ҜНЁРЕ·ўХ№¶Ф»щҙшҙҰАн¶аМеЦЖ¶аФШІЁөДҙ«КдТӘЗуЈ¬ЙијЖБЛТ»ЦЦЎ°N+1ЎұөДКэЧЦЗ°¶ЛИЪәПКХ·ўБҙВ·ЎЈ·ЦОцәНІыКцБЛБҙВ·ЦРёчёцЦчТӘДЈҝйөДКэС§ФӯАнәНУЕ»ҜЙијЖЈ¬ј«ҙуөШҪөөНБЛЖдФЪКэЧЦ»щҙшЙијЖЦРөДЧКФҙПыәДЈ¬ФЪ№ӨіМЙијЖЦРҪбәПөзФҙҝШЦЖјјКхҪшТ»ІҪҪөөНДЈҝй№ҰәДЎЈёГКэЧЦЗ°¶ЛБҙВ·Ҫб№№ҫЯұёБй»о¶аұдөДҝЙЕдЦГМШРФЈ¬НЁ№э·ВХж·ЦОцБЛКХ·ўБҙВ·ФЪІ»Н¬іЎҫ°ПВөД·щЖөПмУҰәНEVM өИІОКэМШРФЎЈҝЙТФҝҙіцЈ¬КХ·ўБҙВ·өД·щЖөПмУҰҫщВъЧгёчёціЎҫ°өДК№УГЈ¬EVM ¶с»ҜТІҪПөНЈ¬¶ЁөгЛг·ЁУлёЎөгЛг·ЁПаЖҘЕдЈ¬НкИ«ВъЧг№ӨіМЙијЖТӘЗуЎЈ