ЛжЧЕПЦҙъНЁРЕјјКхөДСёЛЩ·ўХ№Ј¬РЕәЕөДөчЦЖ·ҪКҪПт¶аСщ»Ҝ·ўХ№Ј¬ҪвФЁјјКхТІЛжЦ®І»¶ППтЗ°·ўХ№ЎЈОӘБЛ¶ФёЯЛЩҙуҙшҝнөДРЕәЕҪшРРКөКұҪвөчЈ¬ПЦФЪәЬ¶аөДҪвөч№ШјьЛг·Ё¶јКЗФЪёЯЛЩУІјюЙПУГҝЙұаіМВЯјӯЖчјю(FPGA)Кө№ЫЈ¬АыУГFPGAЗҝҙуөДЧКФҙәНКөКұҙҰАнДЬБҰАҙҝмЛЩөДКөПЦРЕәЕөДёъЧЩЎўЛш¶ЁәНҪвөчө«КЗЈ¬»щУЪУІјюөДКөПЦ·Ҫ°ёәН»щУЪИнјюөД·Ҫ°ёПаұИЈ¬НщНщҙжФЪІ»ДЬСёЛЩККУҰөчЦЖСщКҪёДұдөДОКМвЎЈОӘБЛУРР§хъҫцХвёцОКМвЈ¬ұКХЯНЁ№э»щПВFPGAІҝ·Ц¶ҜМ¬о®ЦШ№№јјКхЈ¬МбіцБЛПаУҰөДҪвҫц·Ҫ°ёЎЈ

1 FPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхҪйЙЬ

ҙУҫЕБгДкҙъТФАҙЈ¬ЛжЧЕFPGAРҫЖ¬јјКхөДЦрІҪіЙКмәН·ўХ№Ј¬FPGAФЪёчёцБмУтЦРөДУҰУГЦрҪҘА©ҙуЈ¬РҫЖ¬ДЪІҝөДЧКФҙ№жДЈТІіЙұ¶ФцјУЎЈө«КЗЈ¬ЛжЧЕFPGAИЭБҝөДА©ҙуЈ¬FPGAөДЙијЖәНКөПЦТІҪҘҪҘіцПЦБЛПВГжөДЖҝҫұОКМвЈә

1)FPGAРҫЖ¬ДЪІҝІјПЯЛжЧЕЙијЖёҙФУ¶ИөДФцјУЈ¬ІјПЯөДДС¶ИіЙЖҪ·ҪФцјУЈ¬ІјПЯөДКұјдТІіЙұ¶ФцјУЎЈ

2)¶ФУЪҙуИЭБҝөДFPGAЈ¬ОӘБЛұЈЦӨЙијЖКұФј¶ЁөДРФДЬЈ¬ОӘБЛВъЧгКұРтФјКшМхјюЈ¬ЧоЦХКөПЦ°жұҫөДКөјКЧКФҙАыУГВК·ҙ¶шПВҪөЎЈ

3)ҙуИЭБҝөДFPGAТ»ө©ЙијЖНкіЙә󣬶ФЖдҪшРРІҝ·ЦДЈҝйөДөчХыәНУЕ»ҜҫӯіЈРиТӘәЬіӨКұјдЎЈ

ФЪҙЛЙПКцХвР©ФӯТтөД»щҙЎЙПЈ¬FPGAөДЦШЕдЦГјјКхУҰРи¶шЙъЎЈFPGAЦШЕдЦГјјКх·ЦОӘНкИ«ЦШЕдЦГјјКхәНІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхБҪЦЦЎЈЖдЦРFPGAНкИ«ЦШЕдЦГјјКхҫНКЗНЁ№эFPGAНвІҝөДЕдЦГҙҰАнөҘФӘЈ¬НЁ№э¶ФFPGAЕдЦГ№ЬҪЕөДұаіМЈ¬АҙКөПЦХыёцFPGAДЪИЭөДЗР»»Ј¬ХвЦЦ·ҪКҪФЪДҝЗ°ТСҫӯөГөҪБЛҪПОӘ№г·әөДУҰУГЎЈ¶шFPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхКЗНЁ№эFPGAДЪІҝ»тНвІҝөДЕдЦГҙҰАнөҘФӘЈ¬¶ФFPGAДЪІҝІҝ·ЦЧКФҙөДКұ·ЦёҙУГЈ¬АҙКөПЦFPGAДЪІҝІҝ·ЦДЈҝйөДЗР»»ЎЈ

¶ФХвБҪЦЦЕдЦГјјКхҪшРРұИҪПЈ¬ҝЙТФҝҙөҪFPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДУЕКЖФЪУЪТФПВХвР©·ҪГжЈә

1)МбёЯБЛЕдЦГЛЩ¶ИЎЈНкИ«ЦШЕдЦГРиТӘЕдЦГХыёцFPGAөДұИМШБчОДјюЈ¬¶шІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхЦ»РиТӘЕдЦГПаУҰДЈҝйөДВЯјӯДЪИЭЈ¬ОДКІҙуРЎПаІоРьКвЈ¬ФЪПаН¬өДЕдЦГКұЦУЖөВКПВЈ¬Іҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДЕдЦГЛЩ¶ИКЗНкИ«ЕдЦГөДјё·ЦЦ®Т»»тХЯјёК®·ЦЦ®Т»ЎЈ

2)КЎВФБЛНкИ«ЕдЦГәуөДёҙО»ЎўПВҙпІОКэөДБчіМЎЈНкИ«ЦШЕдЦГФЪЕдЦГНкіЙәуЈ¬ХыёцFPGAҙҰУЪіхКјЧҙМ¬Ј¬РиТӘЦШРВ¶ФҪУҝЪҪшРРіхКј»ҜЈ¬ІўЕдЦГФЛРРІОКэЎЈ¶шІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхІ»УГҪшРРИ«ҫЦёҙО»Ј¬ПВҙпІОКэТІЦ»РиТӘХл¶ФЦШ№№өДДЈҝйЎЈ

3)ұЈҙжБЛFPGAФЛРРөДЦРјдҪб№ыәНКэҫЭЎЈНкИ«ЦШЕдЦГәЬДСұЈҙжFPGAФЛРРөДЦРјдҪб№ыЈ¬Из№ыНвҪУDDR SDRAMөИҙжҙўөҘФӘЈ¬ТІ»бТтОӘҪУҝЪөДЦШРВёҙО»¶шөјЦВКэҫЭ»мВТЈ¬¶шІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхНкИ«І»УГөЈРДХвР©ОКМвЎЈ

Іҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхҫЯУРЙПКцПа¶ФУлНкИ«ЦШЕдЦГјјКхөДУЕКЖНвЈ¬ТІәННкИ«ЦШЕдЦГјјКхТ»СщЈ¬ҫЯУРөН№ҰәДәНБй¶ҜРФёЯөДУЕөгЈ¬ІўЗТҫЯұёФ¶іМјУФШ№ҰДЬЈ¬ҝЙТФНЁ№эУРПЯНшВз»тХЯОЮПЯНшВзАҙКөПЦі¬ҫа»·ҫіПВөДFPGA№ҰДЬұдёьЎЈ

Іҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхәННкИ«ЦШЕдЦГјјКхПаұИЈ¬¶ФFPGAЙијЖИЛФұөДҝӘ·ўДЬБҰәН№ж»®ДЬБҰТӘЗуёьёЯЈ¬ПВГжНЁ№э¶ФТ»ёцјтөҘөДКэЧЦРЕәЕҪвөчПөНіЈ¬АҙёшіцІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДКөПЦНҫҫ¶ЎЈ

2 FPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДУІјюКөПЦ·Ҫ°ё

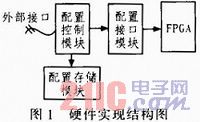

FPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№өДУІјюКөПЦИзНј1ЛщКҫЈ¬ОӘБЛұЈЦӨFPGAЕдЦГөДҝЙҝҝРФЈ¬ұҫОДІЙУГБЛFPGAНвІҝөҘФӘҝШЦЖЕдЦГБчіМөДКөПЦ·ҪКҪЎЈТ»ёц»щұҫөДКөПЦҪб№№іэБЛұ»ЕдЦГөДFPGAНвЈ¬РиТӘУРЕдЦГҝШЦЖДЈҝйЎўЕдЦГҪУҝЪДЈҝйәНЕдЦГҙжҙўДЈҝйХв3ёцІҝ·ЦЎЈЖдҪнЕдЦГҝШЦЖДЈҝйТ»°гУЙDSPЎўөҘЖ¬»ъЎўARMҙҰАнЖч»тХЯPowerPCСЎФсЈ¬ЦчТӘ№ҰДЬКЗҙУЕдЦГҙжҙўДЈҝй»тХЯНвІҝҪУҝЪЦР»сИЎЕдЦГұИМШБчОДјюЈ¬ІўФЪРиТӘІҝ·Ц¶ҜМ¬ЦШ№№өДКұҝМ°СЕдЦГұИМШБчОДјюҙ«ЛНөҪЕдЦГҪУҝЪДЈҝйЎЈЕдЦГҪУҝЪДЈҝйТ»°гУЙFPGA»тХЯCPLDКөПЦЈ¬№ҰДЬКЗҪУКХЕдЦГҝШЦЖДЈҝйҙ«КдөДЕдЦГұИМШБчЈ¬ҪшРРПаУҰөДКұРтЧӘ»»Ј¬ІъЙъВъЧгFPGAЕдЦГКұРтөДРЕәЕЈ¬ҙУ¶ш¶ФFPGAҪшРРЕдЦГЎЈЕдЦГҙжҙўДЈҝйТ»°гКЗFLASH»тХЯSDRAMЈ¬ҝЙТФіӨЖЪ»тХЯБЩКұұЈҙж¶аёцЕдЦГұИМШБчОДјюЎЈ

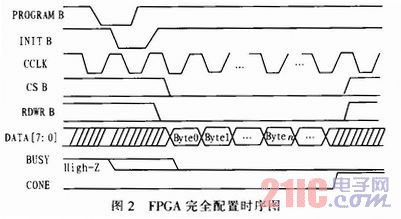

ФЪНј1өДҪб№№ЦРЈ¬ЕдЦГҪУҝЪДЈҝйКЗКөПЦөД№ШјьДЈҝйЈ¬ёщҫЭЕдЦГЛЩ¶ИәНОИ¶ЁРФөДТӘЗуЈ¬ҝЙТФІЙУГSlave SelectMap»тХЯSlave SetialЕдЦГДЈКҪЈ¬ҙУРФДЬҝјВЗЈ¬Т»°гСЎФсSlave SelectMapХвЦЦІўРРЕдЦГДЈКҪЈ¬ФЪЕдЦГКұЦУЧоёЯ50MHzЎўЕдЦГ№ЬҪЕ32О»өДЗйҝцПВЈ¬ЕдЦГЛЩ¶ИҝЙТФҙпөҪ1Ј®6Gb psЎЈФЪSlave SelectMapДЈКҪПВЈ¬ЕдЦГҪУҝЪДЈҝйәНFPGAөД№ЬҪЕБ¬ҪУҝЙТФІОҝјXilinxVinex-5 Configuration User GuideЦРПаУҰХВҪЪЈ¬ұҫОДІ»ФЩЧёКцЎЈІўёщҫЭИзНј2ЛщКҫөДЕдЦГКұРтЈ¬АҙКөПЦFPGAНкИ«ЕдЦГұИМШБчОДјюөДПВФШәН№ҰДЬКөПЦЎЈ

ФЪҪшРРЕдЦГІҝ·Ц¶ҜМ¬ҝЙЦШ№№ұИМШБчОДјюКұЈ¬ТтОӘёГұИМШБчОДјюІ»ПсНкХыөДЕдЦГұИМШБчОДјюТ»СщҫЯУРОДјюН·Ј¬¶шКЗЦ»УРЦЎөШЦ·ЎўЕдЦГКэҫЭј°РЈСйәНЈ¬өұЛщУРЕдЦГДЪИЭҙ«КдөҪFPGAәуЈ¬І»»бУРDONEРЕәЕАӯёЯАҙұнКҫЕдЦГҪбКшЎЈФЪХвЦЦЗйҝцПВЈ¬ұШРлјаКУҙ«КдАҙөДЕдЦГКэҫЭЈ¬өұіцПЦІҝ·ЦЦШЕдЦГОДјюөДҪбКшұкЦҫDESYNCH(0000000D)КұЈ¬ҫНҝЙТФЕР¶ПІҝ·ЦЦШ№№БчіМҪбКшЈ¬ҝЙТФФЛРРРВөДЦШ№№ДЈҝйЎЈ

3 »щУЪFPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№өДРЕәЕҪвөчПөНіҝӘ·ўБчіМ

3Ј®1 FPGAДЈҝй»®·Ц

ФЪНкіЙБЛЦ§іЦFPGAІҝ·Ц¶ҜМ¬ҝЙЦШ№№өДУІјюКөПЦәуЈ¬ПВГжҝӘКј№ж»®РЕәЕҪвөчПөНіөДFPGAЙијЖјЬ№№ЎЈИзНј3ЛщКҫЈ¬РЕәЕҪвөчПөНіЦчТӘУЙРЕөА»ҜДЈҝйЈ¬ҝЙЦШ№№ҪвөчДЈҝйәНКэҙ«ҪУҝЪДЈҝйЧйіЙЎЈ

РЕөА»ҜДЈҝйЦчТӘКЗ°СADКэҫЭҪшРРРЕөА»ҜҙҰАнЈ¬ҪшРРВЛІЁЈ¬ПВұдЖөЎўРЕөАСЎФсәНійИЎЎЈҝЙЦШ№№ҪвөчДЈҝйКЗХл¶ФІ»Н¬өчЦЖСщКҪөД·ЦұрКөПЦІ»Н¬өДҪвөчДЈҝйЈ¬ІўёщҫЭКөјКРиТӘҪшРРІҝ·ЦЦШ№№ЎЈКэҙ«ҪУҝЪДЈҝйКЗ°СҪвөчөДҪб№ыҙ«КдөҪFPGAНвЈ¬ҪшРРәуРшҙҰАнәНФЪҪзГжЦРПФКҫЎЈ

3Ј®2 FPGAДЈҝйөДЙијЖәНКөПЦ

°ҙХХНј3ЛщКҫөДҪб№№Ј¬°ҙХХПВГжІҪЦиҪшРР»щУЪІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДFPGAіМРтЙијЖЈә

1)°СРиТӘІҝ·ЦЦШ№№өДFPGAДЈҝйЙијЖОӘТ»ёцҝХәРЈ¬јҙЦ»УРКдИлКдіц№ЬҪЕЈ¬Г»УРКөјКДЪИЭөДҝХДЈҝйЎЈФЪҪшРРҝХДЈҝйөД№ЬҪЕ№ж»®КұТӘЧЫәПҝјВЗ¶аЦЦҪвөчСщКҪПВөДҪУҝЪјжИЭРФЈ¬ұЈЦӨТ»ёцДЈҝйҪУҝЪДЬәӯёЗРиТӘҙҰАнөДЛщУРСщКҪЎЈ

2)·ЦұрНкіЙІ»РиТӘІҝ·ЦЦШ№№өДFPGAУиДЈҝйЈ¬ІўНкіЙFPGA¶ҘІгДЈҝйЎЈ

3)¶ФFPGA¶ҘІгДЈҝйҪшРРЧЫәПЈ¬ІъЙъ¶ҘІгНшұнЎЈ

4)°ҙХХІҪЦи1)ЦРөДДЈҝй¶ЁТеёсКҪНкіЙХл¶ФІ»Н¬өчЦЖДЈКҪөДҪвФЁДЈҝйЈ¬Изqpsk_demodЈ¬fsk_demodөИЈ¬ІўНЁ№э·ВХжСйЦӨЈ¬И»әуЦрДЈҝй·ЦұрЧЫәПіЙөҘ¶АөДДЈҝйНшұнОДјюЈ¬ұЈҙжөҪІ»Н¬өДДҝВјЦРЎЈ

5)ФЪPlanAhead№ӨҫЯЦРөјИлFPGA¶ҘІгНшұнЈ¬ЧўТвФЪөјИлСЎПоЦРСЎФсЦ§іЦІҝ·ЦЦШ№№ЎЈФЪPlanAhead№ӨҫЯЦР°С2ёцҝХөДҝЙЦШ№№ҪвөчДЈҝйЙи¶ЁОӘҝЙЦШ№№·ЦЗш(ReconfigurablePartition)Ј¬ИзНј4ЛщКҫЈ¬Іў°СІҪЦи4)ЦРЧЫәПәГөДДЈҝйНшұнЦё¶ЁОӘҝЙЦШ№№ДЈҝйПВөДҝЙСЎДЪИЭЎЈ

6)ФЪPlanAhead№ӨҫЯөДDeviceКУНјЦРЈ¬¶ФҝЙЦШ№№ДЈҝй»®·Ц·ЦЗш(PBlock)Ј¬ДҝЗ°·ЦЗшЦ»Ц§іЦҫШРОЈ¬ТӘЗу·ЦЗш°ьә¬өДЧКФҙКэДҝВФҙуУЪҪвФЁДЈҝйЛщРиЧКФҙөДЧоҙуЦөЈ¬ЖдЦР°ьАЁВЯјӯЧКФҙ(ІйХТұнәНјДҙжЖч)Ј¬іЛ·ЁЖч(DSP48E)әНRAMЧКФҙЎЈ

7)ёщҫЭ¶Ф2ёцҝЙЦШ№№ҪвөчДЈҝйөДІ»Н¬ЕдЦГЈ¬ІъЙъ¶аёцЕдЦГОДјюЈ¬ЕдЦГОДјюөДТ»ёцАэЧУИзұн1ЛщКҫЈ¬ІўЦрТ»ҪшРРІјҫЦІјПЯЈ¬ІъЙъНкХыөДЕдЦГұИМШБчОДјюәНУГУЪІҝ·ЦЦШ№№өДұИМШБчОДјюЎЈ¶ФУЪГҝТ»ЧйЕдЦГОДјюЈ¬»бІъЙъТ»ёц°ьә¬ҫІМ¬ВЯјӯөДНкХыЕдЦГұИМШБчОДјюЈ¬әН2ёцУГУЪІҝ·ЦЦШ№№өДұИМШБчОДјюЈ¬·Цұр¶ФУҰ2ёцІ»Н¬өД·ЦЗшЈ¬ЕдЦГјУФШКұІ»ДЬЛжұг»Ҙ»»ЎЈ

8)¶Фұн1ЦРЕдЦГОДјюҪшРРЙијЖ№жФтјмІйұИҪПЈ¬ұЈЦӨёчЧйЕдЦГОДјюЙъіЙөДНкХыЕдЦГөДұИМШБчОДјюКЗТ»ЦВөДЎЈ

9)НкіЙТФЙПЙијЖәуЈ¬КЧПИөчУГИОТвТ»ёцНкХыЕдЦГОДјюҪшРРјУФШЈ¬ұЈЦӨFPGAіЙ№ҰФЛРРҫІМ¬ВЯјӯЈ¬И»әуёщҫЭРиТӘЈ¬СЎФсұн1ЦРөДЕдЦГОДјюұнЦРөДИОәО1ЧйЈ¬ҪшРРІҝ·Ц¶ҜМ¬јУФШЎЈ

4 УҰУГҪб№ы

ТФЙПЙијЖҫӯ№эКөјКСйЦӨЈ¬ҝЙТФКөПЦ2В·РЕәЕФЪІ»Н¬өчЦЖСщКҪөДҪвөчЈ¬өұРЕәЕСщКҪұд»ҜКұЈ¬¶ҜМ¬јУФШПаУҰөДҪвөчДЈҝйЈ¬ҝЙТФСёЛЩНкіЙ№ҰДЬЗР»»Ј¬КөПЦ¶ФУҰөДҪвөч№ҰДЬЎЈҫӯ№эКөјКІвКФЈ¬Іҝ·Ц¶ҜМ¬ҝЙЦШ№№ДЈҝйөДјУФШЛЩ¶Иҙж10 msТФДЪЈ¬ј«ҙуөДМбёЯБЛФӯУРПөНіөДРФДЬЎЈ

5 ҪбВЫ

ДҝЗ°№ъјКЙП¶ФFPGAҝЙЦШ№№јјКхөДСРҫҝј«ОӘ№г·әЈ¬ұҫОДҪйЙЬБЛТ»ЦЦ»щУЪXilinx FPGAөДІҝ·Ц¶ҜМ¬ҝЙЦШ№№јјКхөДРЕәЕҪвөчПөНіЈ¬ҝЙТФ°СІ»Н¬өДҪвөчДЈҝй¶ЁО»өҪРҫЖ¬ДЪІҝН¬Т»ВЯјӯЧКФҙІҝ·ЦЈ¬НЁ№эЦШ№№ХвР©ЧКФҙАҙКөПЦІ»Н¬СщКҪРЕәЕөДҪвөчЈ¬Н¬КұұЈіЦЖдЛыІҝ·ЦөзВ·№ҰДЬХэіЈФЛРРЈ¬ҙУ¶шМбёЯБЛПөНіөДККУҰДЬБҰЎЈ

ЎЎЎЎұҫПөНіҝЙТФҙжНЁРЕПөНіЦРөГөҪУҰУГЈ¬¶ФәҪМмЎўөзБҰөИБмУтөДАаЛЖПөНіТІУРІОҝјјЫЦөЈ¬ҝЙТФМбёЯПаУҰПөНіөДБй»оРФәНА©Х№РФЈ¬јхөНПөНі№ҰәДЈ¬Лх¶МПөНіҝӘ·ўКұјдЎЈ