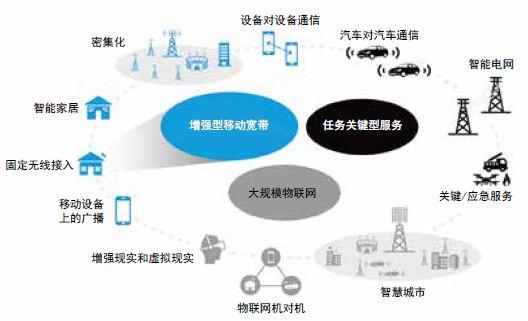

ПВТ»ҙъ5GНшВзөДФёҫ°КЗЈәПаұИПЦУРөД4GНшВзЈ¬ФЪИЭБҝЎўёІёЗ·¶О§әНБ¬ҪУРФ·ҪГжКөПЦКэБҝј¶МбЙэЈ¬Н¬КұҙуҙуҪөөНФЛУӘЙМәНУГ»§өДГҝұИМШКэҫЭіЙұҫЎЈНј1ПФКҫБЛ5GјјКхәННшВзКөПЦөД¶аПоК№УГ°ёАэәН·юОсЎЈ

5GРВОЮПЯөз(NR)ұкЧј»ҜөЪТ»ҪЧ¶ОөДЦШөгКЗ¶ЁТеТ»ЦЦОЮПЯөзҪУИлјјКх(RAT)Ј¬АыУГРВөДҝнҙшЖөВК·ЦЕд(°ьАЁ

6GHzТФПВәН24GHzТФЙПөДЖө¶О)Ј¬ТФКөПЦ№ъјК

ТЖ¶ҜНЁРЕ2020Дкј°Ц®әуөДФёҫ°Х№НыЦРМбіцөДҙу·еЦөНМНВБҝәНөНСУКұЎЈ

Нј1Јә

5GК№УГ°ёАэ

НЁ№эАыУГNR RATЈ¬УИЖдКЗФЪәБГЧІЁЖө¶О·ҪГжКөПЦөДёДҪшЈ¬ТЖ¶ҜНшВзФЛУӘЙМЦ»Ри»Ё·Сҙ«НіөзАВәН№вПЛөҪ»§ЙиК©өДТ»РЎІҝ·ЦКұјдәНіЙұҫЈ¬јҙҝЙПтјТНҘЎў№«ФўәНЖуТөМṩǧХЧ№М¶ЁОЮПЯҪУИл(FWA)·юОсЎЈФЛУӘЙМ»№Ҫ«FWAЧчОӘМṩХжХэ

ТЖ¶ҜҝнҙшМеСйөДКФСйЖҪМЁЎЈТвБПЦ®ЦРөДКЗЈ¬VerizonЎўAT&TТФј°ЖдЛыФЛУӘЙМХэФЪҙуБҰҝӘХ№FWAКФСйЈ¬ДҝұкКЗФЪ2019ДкКөПЦНкИ«ЙМТө»ҜЎЈ

ұҫІҝ·Ц·ЦОцБЛМṩЙПКцРВРНәБГЧІЁFWA·юОсЛщРиөДјЬ№№Ј¬ТФҪјЗшІҝКрОӘАэМЦВЫБЛБҙВ·ФӨЛгТӘЗуЈ¬ҪйЙЬБЛУГУЪ»щХҫКХ·ўРЕ»ъ(BTS)өД»мәПІЁКшіЙРНјјКхУлИ«КэЧЦІЁКшіЙРНјјКхөДМШөгәНБҪХЯЦ®јдөДИЁәвЈ¬Іў·ЦОцБЛКөПЦХвБҪЦЦјјКхөД°лөјМејјКхЎЈ

FWAІҝКр

К№УГәБГЧІЁөДТ»ёцГчПФУЕКЖКЗДЬ№»ТФҪПөНіЙұҫАыУГҙЛЗ°Оҙід·ЦАыУГөДБ¬РшЖөЖЧЎЈХвР©Жө¶ОҝЙКөПЦёЯҙп400MHzөДФШІЁҙшҝнЈ¬ЗТЙМУГBTSЙијЖОӘІЙУГЦ§іЦЧоёЯ1.2GHzЛІКұҙшҝнөДФШІЁҫЫәПЎЈУГ»§¶ЛЙиұё(CPE)Ҫ«Ц§іЦі¬№э2GbpsөД·еЦөЛЩВКЈ¬ІўҫЯУР¶аЦЦНвРОіЯҙзЈәИ«КТНв·ЦМеКҪ°ІЧ°РНЎўИ«КТДЪЧАГжРНәНdongleРНЎЈЛжәу»№Ҫ«НЖіц

ТЖ¶Ҝөз»°РНЦХ¶ЛЎЈ

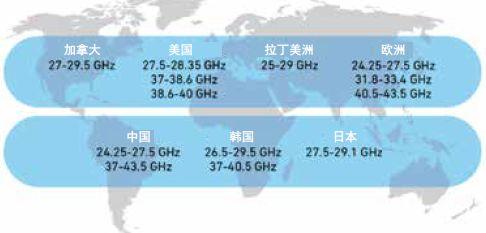

И«ЗтәБГЧІЁЖөЖЧҝЙУГРФИзНј2ЛщКҫЎЈФЪГА№ъЈ¬ҙуІҝ·ЦКФСй¶јКЗФЪЦ®З°өД27.5ЦБ28.3

5GHzLMDSЖө¶О·¶О§ЦРҪшРРЈ¬ө«ФЛУӘЙМјЖ»®ФЪёьҝнөД39GHzЖө¶О(ТСФЪёьҙуөДҫӯјГЗшУт»сөГРнҝЙ)ЦРҪшРРИ«№ъІҝКрЎЈ3GPPТСҫӯ·ЦЕдБЛХвР©әтСЎЖө¶ОЈ¬ІўЗТіэБЛ28GHzЈ¬ёчәтСЎЖө¶ОҪ«УЙ№ъјК

өзРЕБӘГЛФЪИ«ЗтҪшРРРӯөчЎЈ

Нј2ЈәИ«Зт24GHzТФЙПөД

5GЖө¶О

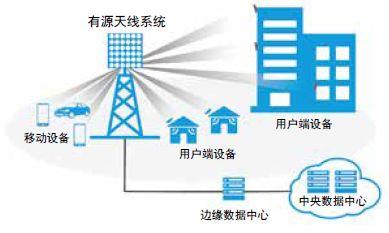

FWAГиКцБЛТ»ёцјҜЦРөД·ЦЙИЗшөДBTSУл¶аёц№М¶Ё»т

ТЖ¶ҜУГ»§Ц®јдөДОЮПЯБ¬ҪУ(Нј3)ЎЈПөНіЙијЖОӘАыУГПЦУРөДЛюХҫЈ¬ІўЦ§іЦөНіЙұҫЧФЧ°КҪCPEА©ҪЁЎЈОӘБЛұЈіЦҪПөНөДіхЖЪІҝКріЙұҫІўҙЩіЙFWAөДЙМТө»ҜЈ¬ХвБҪХЯ¶јЦБ№ШЦШТӘЎЈіхЖЪІҝКрЦчТӘОӘКТНвөҪКТНвІҝКрЈ¬ІўІЙУГЧЁТөөДОЭ¶Ҙ°ІЧ°·ҪКҪЈ¬ҝЙЧоҙуПЮ¶ИөША©ҙуёІёЗ·¶О§Ј¬ҙУ¶шИ·ұЈЧоіхөДҝН»§ВъТв¶ИЈ¬Н¬КұК№BTSәНCPEЙиұёУРКұјдКөПЦЛщРиөДіЙұҫәНРФДЬДҝұкЎЈ

Нј3Јә¶ЛөҪ¶ЛFWAНшВз

ҪПҙуөДёІёЗ·¶О§¶ФУЪіЙ№ҰКөПЦFWAЙМТө»ҜЦБ№ШЦШТӘЎЈОӘБЛЛөГчХвТ»өгЈ¬ОТГЗЙиПлФЪТ»ёцГҝЖҪ·Ҫ№«АпУР800ёцјТНҘөДҪјЗшҪшРРІҝКрЈ¬ИзНј4ЛщКҫЎЈ¶ФУЪХҫөгјдҫаАл(ISD)ОӘ500mөДBTSЈ¬ОТГЗРиТӘЦБЙЩ9ёц·дОСХҫөгөД20ёцЙИЗшЈ¬ГҝёцЙИЗшёІёЗ35ёцјТНҘЎЈјЩЙи33%өДУГ»§З©ФјК№УГ1Gbps·юОсЈ¬ЗТНшВзі¬¶оАыУГВКОӘДҝЗ°өД5ұ¶Ј¬ФтЛщРиөДЖҪҫщBTSЧЬИЭБҝОӘГҝёцЙИЗш3GbpsЎЈјЩЙиЖҪҫщЖөЖЧР§ВКОӘ2bps/HzЈ¬ЗТҝХјдёҙУГІгКэОӘ4Ј¬ФтАыУГ400MHzөДҙшҝнҫНҝЙТФВъЧгХвТ»ИЭБҝРиЗуЎЈИз№ыУГ»§ГҝёцФВЦ§ё¶100ГАФӘөД·СУГЈ¬ФтДкКХИлҪ«ОӘ280,000ГАФӘ/ЖҪ·Ҫ№«Ап/ДкЎЈөұИ»Ј¬Из№ыІ»ҝјВЗЦШёҙіЙұҫЈ¬ОТГЗІ»М«ЗеіюFWAКЗІ»КЗТ»ёцәГөДЙМТөДЈКҪЈ¬ө«ОТГЗҝЙТФөГіцТФПВҪбВЫЈәөұISDФцјУКұЈ¬ХвёцЙМТөУГАэ»бУРЛщёДЙЖЎЈОӘҙЛЈ¬ФЛУӘЙМТӘЗуЙиұё№©УҰЙМ№№ҪЁДЬ№»ФЪЧоёЯ№ж¶ЁПЮЦөПВФЛРРөДBTSәНCPEЙиұёЈ¬ТФЧоҙуПЮ¶ИөШМбёЯёІёЗВКәНУҜАыДЬБҰЎЈ

Нј4ЈәіЗКРҪјЗш»·ҫіЦРөДFWA

ГА№ъБӘ°оНЁРЕОҜФұ»бТСҫӯОӘ28әН39GHzЖө¶О¶ЁТеБЛ·ЗіЈёЯР§өДИ«Пт·шЙд№ҰВК(EIRP)Ј¬Изұн1ЛщКҫЎЈХвСщТ»АҙЈ¬ФЪФЛУӘЙМФӨЖЪөДіЙұҫЎўіЯҙзЎўЦШБҝәН№ҰВКФӨЛг·¶О§ДЪ№№ҪЁ·ыәПХвР©ДҝұкТӘЗуөДПөНііЙОӘТ»ҙуМфХҪЎЈСЎФсККөұөДЗ°¶ЛјЬ№№әНRF°лөјМејјКхКЗУҰ¶ФХвТ»МфХҪөД№ШјьЎЈ

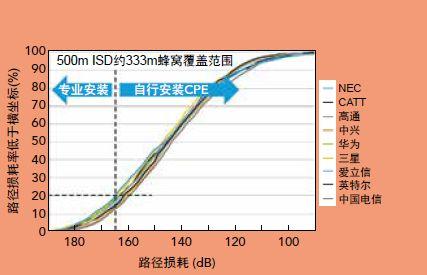

FWAБҙВ·ФӨЛг

ұкЧј»ъ№№Т»ЦұФЪГҰУЪ¶ЁТеРФДЬТӘЗуЈ¬ТФј°ЖА№АёчЦЦәБГЧІЁЖөВКөДУГАэЎЈіЗКРәкіЎҫ°КЗөдРНFWAІҝКрөДЧојСұнПЦРОКҪЈәҫЯУРҪПҙуөДISD(300ЦБ500m)Ј¬ІўМṩҪПёЯөДВ·ҫ¶ЛрәДФӨЛгЈ¬ҝЙҝЛ·юәБГЧІЁЖөВК·¶О§ДЪУцөҪөДРн¶аҙ«ІҘМфХҪЎЈОӘёгЗеЛщРиөДБҙВ·ФӨЛгЈ¬ОТГЗІЙУГБЛҝЙЛөГч·ЗКУПЯХҫөгМхјюәНКТНвЦБКТДЪҙ©НёРФөДҙу№жДЈҫ«ПёРЕөАДЈРН(Из3GPP¶ЁТеөДДЈРН)ҪшРРВ·ҫ¶ЛрәДНіјЖДЈДвЎЈНј5ПФКҫБЛЙиұё№©УҰЙМәНФЛУӘЙМФЪ500m ISDіЗКРәк»·ҫіПВҪшРРІҝКрөДҪб№ыЎЈФЪХвёцДЈДвІҝКрЦРЈ¬ОТГЗІЙУГБЛ28GHzРЕөАДЈРНЈ¬ЖдЦРКТДЪУГ»§әНКТНвУГ»§·ЦұрХј80%әН20%ЎЈФЪКТДЪУГ»§ЦРЈ¬50%ІЙУГёЯҙ©НёЛрәДДЈРНЈ¬50%ІЙУГҪПөНЛрәДДЈРНЎЈҙУіӨФ¶ҪЗ¶ИАҙЛөЈ¬ФЛУӘЙМПЈНыЗұФЪөДУГ»§ЦРЦБЙЩ80%ҝЙЧФРР°ІЧ°Ј¬ТФЧоҙуПЮ¶ИөШјхЙЩіЙұҫёьёЯөДЧЁТөОЭ¶Ҙ°ІЧ°ЎЈ·ЦІјЗъПЯұнГчЈ¬ПөНіөДЧоҙуВ·ҫ¶ЛрәДОӘ165dBЎЈ

Нј5ЈәISDОӘ500mөДіЗКРәкХҫ»·ҫіПВөДВ·ҫ¶ЛрәДДЈДвНіјЖЎЈ

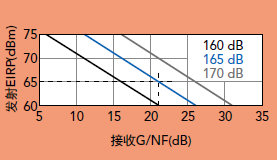

ұХәПБҙВ·ИЎҫцУЪ¶аёцұдБҝЈ¬°ьАЁ·ўЙдEIRPЎўҪУКХМмПЯФцТжЎўҪУКХЖчФлЙщПөКэ(NF)әНЧоРЎұЯФөёІёЗНМНВБҝЎЈОӘұЬГв№э¶ИЙијЖіЙұҫГфёРРНCPEЙиұёЈ¬ТФј°Ҫ«ёәөЈЧӘТЖЦБBTSЈ¬БҙВ·ЙијЖУҰҙУCPEҪУКХЖчҝӘКјЈ¬ІўІЙУГ·ҙПтНЖөјөД·Ҫ·ЁҙпөҪBTS·ўЙдЖчТӘЗуЎЈОӘБЛҙъМжҙ«НіөДG/T(ЛжПөНіФлЙщОВ¶Иұд»ҜөДМмПЯФцТжВК)Ж·ЦКТтКэ(FOM)Ј¬ОТГЗ¶ЁТеБЛТ»ёцёьұгАыөДG/NF FOMЈәНЁ№эҪУКХЖчөДNFҪшРР№йТ»»ҜҙҰАнөД·еЦөМмПЯФцТж(°ьАЁІЁКшіЙРНФцТж)ЎЈНј6ЛөГчБЛёчЦЦҪУКХG/NFЛщРиөДEIRPЈ¬ТФұгҝЛ·юМṩ1GbpsұЯФөёІёЗНМНВБҝөДДҝұкВ·ҫ¶ЛрәДЎЈХвАпјЩЙиөчЦЖЖөЖЧР§ВКОӘ2bps/HzЈ¬ҪвөчРЕФлұИ(SNR)ОӘ8dBЎЈҙУНјЦРҝЙТФҝҙіцЈ¬ОТГЗҝЙТФИ·¶ЁёчЦЦCPEҪУКХЖчG/NFЛщРиөДBTS EIRPЎЈАэИзЈ¬өұCPEҪУКХЖчG/NFЎЭ21dBiКұЈ¬ТӘФЪВ·ҫ¶ЛрәДОӘ165dBөДМхјюПВО¬іЦ1GbpsөДБҙВ·Ј¬Ҫ«РиТӘ65dBm BTS EIRPЎЈ

Нј6 Јә ·ўЙдEIRPУлҪУКХG/NFПа¶ФУЪ1GbpsұЯФөёІёЗНМНВБҝөДВ·ҫ¶ЛрәДЎЈ

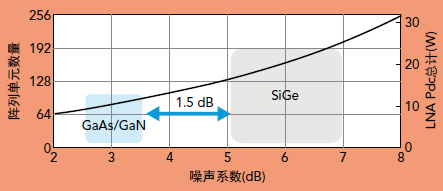

ҪУПВАҙЈ¬ОТГЗҪ«НЁ№эГиКцКөПЦ21dB G/NF(Нј7)ЛщРиөДЧоЙЩХуБРМмПЯөҘФӘЈ¬МҪМЦҪУКХЖчNFөДУ°ПмЎЈОТГЗ»№Ҫ«ҪйЙЬөНФлЙщ·ЕҙуЖч(LNA)өДЧЬ№ҰәДЎЈНЁ№эөчХыЧшұкЦб·¶О§Ј¬ОТГЗҝЙТФҪ«БҪХЯЦШөюЈ¬Іў№ЫІмNF¶ФХуБРҙуРЎЎўёҙФУРФәН№ҰВКөДУ°ПмЎЈФЪХвёцКҫАэЦРЈ¬ГҝёцLNAөД№ҰәДОӘ40mWЈ¬ХвКЗПаҝШХуөДөдРН№ҰәДЎЈНјЦР»№ПФКҫБЛ30GHzЖөВКМхјюПВЈ¬130nm SiGe BiCMOSЎў90nmGaAs PHEMTәН150nm GaN HEMTөДRFFE NFЈ¬°ьАЁT/RҝӘ№ШЛрәДЎЈ»ҜәПОп°лөјМејјКхҝЙҪ«NFҪөөН1.5dB»тТФЙПЈ¬ҙУ¶шҪ«ХуБРҙуРЎЎў№ҰәДДЛЦБCPEіЙұҫјхЙЩ30%ЎЈ

Нј7ЈәХуБРҙуРЎУлЗ°¶ЛNFәН№ҰәДөД№ШПө(G/NF=21dB)

ОӘМҪЛч¶ФRFFEЧйјюјјКхСЎФсәНЙијЖ¶шСФЦБ№ШЦШТӘөДјЬ№№ИЁәвЈ¬ОТГЗПИАҙБЛҪвМмПЯЙЁГиТӘЗуЎЈИ»әуЈ¬ОТГЗ»бЦШөгҪйЙЬөзВ·ГЬ¶ИәН·вЧ°¶ФјҜіЙКҪЛ«ј«»ҜҪУКХ/·ўЙдХуБРөДУ°ПмЎЈЧоәуЈ¬ОТГЗ»бСРҫҝИ«КэЧЦІЁКшіЙРНәН»мәПЙдЖөІЁКшіЙРНјЬ№№Ј¬ТФј°ХвБҪЦЦјЬ№№ёчЧФөДТӘЗуЎЈ

Т»О¬»т¶юО¬ЙЁГи

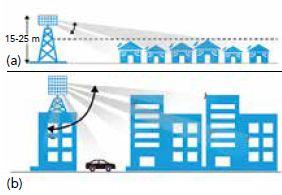

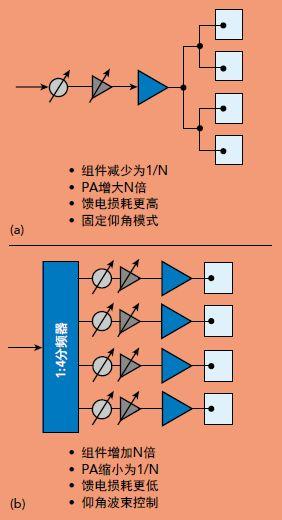

ХуБРЦРУРФҙРЕөАөДКэБҝИЎҫцУЪРн¶аТтЛШЎЈОТГЗПИАҙБЛҪвТ»ПВ·ҪО»ҪЗәНСцҪЗЙЁГиТӘЗуЈ¬ТФј°өдРНөДFWAІҝКрКЗ·сРиТӘК№УГ¶юО¬ІЁКшіЙРНЈ¬Та»тЦ»К№УГёҙФУРФёьөНөДТ»О¬(Ҫц·ҪО»ҪЗ)ІЁКшіЙРНХуБРјҙҝЙЎЈХвёцҫц¶Ё¶Ф№ҰВК·ЕҙуЖч(PA)УРТ»¶ЁУ°ПмЎЈНј8ПФКҫБЛБҪЦЦFWAІҝКріЎҫ°ЎЈФЪҪјЗшІҝКрЦРЈ¬РЕәЕЛюёЯ¶ИОӘ15ЦБ25mЈ¬·дОС°лҫ¶ОӘ500ЦБ1000mЈ¬ЧЎХ¬ЖҪҫщёЯ¶ИОӘ10mЎЈХэИзҙ«НіөДәк·дОСПөНіДЗСщЈ¬ёГІҝКріЎҫ°ЦРОЮРиІЙУГНкИ«ЧФККУҰСцҪЗЙЁГиЎЈНЁ№э№ІН¬АЎөз¶аёцОЮФҙМмПЯөҘФӘЈ¬ҝЙПтПВҫЫҪ№СцҪЗІЁКшЈ¬ИзНј9aЛщКҫЎЈ·шЙдөҘФӘөДҙ№ЦұІгөюБРЦјФЪЧоҙуіМ¶ИөШјхЙЩЧЎХ¬ЙП·ҪөД·шЙдЈ¬ІўёІёЗөШГжЙПөДИОәОБгО»ЗшУтЎЈҙЛНвЈ¬ФцТжДЈКҪЙијЖОӘТФУлВ·ҫ¶ЛрәДПаН¬өДЛЩВКПа¶ФөШФцјУЈ¬ҙУ¶шОӘФ¶ҪьУГ»§МṩёьҫщФИөДНшВзёІёЗЎЈұкіЖ°л№ҰВКІЁКшҝн¶ИҝЙТФҪьЛЖұнКҫОӘ102Ўг/NANTЈ¬¶шХуБРФцТж·щ¶ИОӘ10log10(NANT)+5dBiЎЈҪиЦъОЮФҙМмПЯЧйәПЈ¬ҝЙјҜЦРСцҪЗІЁЈ¬ІўФцјУ№М¶ЁМмПЯФцТжЈ¬Изұн2ЛщКҫЎЈ¶ФУЪҪјЗшFWAІҝКрЈ¬ІЙУГ13ЦБ26ЎгөДІЁКшҝн¶ИҫН№»БЛЈ¬Н¬КұАыУГ4ЦБ8ёцМмПЯөҘФӘөДОЮФҙБРХуБРЧйәПЎЈИ»¶шЈ¬ФЪіЗКРІҝКріЎҫ°ЦРЈ¬СцҪЗЙЁГиТӘЗуёьёЯЈ¬ЗТК№УГөДПөНіҪцПЮУЪ1ЦБ2ёцОЮФҙөҘФӘЎЈ

Нј8ЈәХуБРёҙФУРФИЎҫцУЪІҝКріЎҫ°ЛщРиөДЙЁГи·¶О§ЈәҪјЗш(a)»тіЗКР(b)

Нј9bЛөГчБЛЦрёцөҘФӘАЎөзөДУРФҙХуБРЎЈЦрёцөҘФӘАЎөзөДХуБРәН°ҙБРАЎөзөДХуБРјЬ№№ҫЯУРПаН¬өДМмПЯФцТжЈ¬ө«°ҙБРАЎөзөДХуБРҫЯУР№М¶ЁСцҪЗІЁКшДЈКҪЎЈЦрёцөҘФӘАЎөзөДХуБРЦ§іЦёьҝнөДЙЁГиҪЗ¶ИЈ¬ө«ЛщРиөДPAЎўПаТЖЖчәНҝЙұдФцТжЧйјюКэБҝКЗ°ьә¬4ёцөҘФӘөДМмПЯөД4ұ¶ЎЈОӘКөПЦПаН¬өДEIRPЈ¬УГУЪЗэ¶ҜУЙ4ёщМмПЯЧйіЙөД°ҙБРАЎөзХуБРөДPAРиТӘМṩЦБЙЩ4ұ¶өДКдіц№ҰВКЈ¬¶шХвәЬИЭТЧёДұд°лөјМеСЎФсЎЈОТГЗУРАнУЙИПОӘЈ¬ҪјЗшBTSҪ«К№УГОЮФҙМмПЯФцТжұИіЗКРІҝКрёЯ6ЦБ9dBөДМмПЯЎЈТтҙЛЈ¬ПаҝШХуЦ»РиёьЙЩөДУРФҙРЕөАЈ¬ҫНДЬ№»КөПЦПаН¬өДEIRPЈ¬ҙУ¶шПФЦшјхЙЩБЛУРФҙЧйјюКэБҝІўҪөөНБЛјҜіЙёҙФУРФЎЈ

Нј9Јә°ҙБРАЎөзөДУРФҙХуБР(a)әНЦрёцөҘФӘАЎөзөДУРФҙХуБР(b)ЎЈ

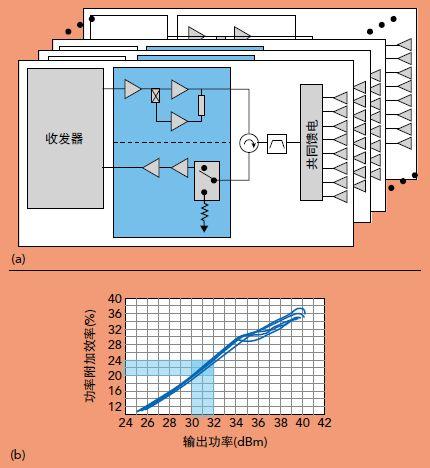

ХуБРЗ°¶ЛГЬ¶И

ФзЖЪөДәБГЧІЁFWA BTSЙијЖІЙУГөҘ¶АөДөҘј«»Ҝ·ўЙдәНҪУКХМмПЯХуБРЈ¬ХвК№өГөзВ·°еУРёь¶аөДҝХјдАҙИЭДЙЧйјюЎЈБнНвЈ¬ХвАаЙијЖұЬГвБЛT/RҝӘ№ШөД¶оНвІеИлЛрәДәНПЯРФ¶ИДСМвЎЈИ»¶шЈ¬К№УГјҜіЙКҪT/RЛ«ј«»ҜХуБРТСіЙОӘјЬ№№·ўХ№өДТ»ҙуЗчКЖ(Нј10)Ј¬ХвК№RFFEГЬ¶ИІ»¶ПФцјУЎЈ№ШјьФӯТтФЪУЪҝХјдПа№ШРФЎЈЧФККУҰІЁКшіЙРНРФДЬИЎҫцУЪҪУКХәН·ўЙдХуБРЦ®јдөДПа¶ФРЈЧјДЬБҰЎЈТтҙЛЈ¬јҜіЙЛ«ј«»Ҝ·ўЙдәНҪУКХРЕөАҫНұдөГ·ЗіЈЦШТӘЈ¬ХвСщХуБРҫНҝЙТФ№ІУГТ»МЧНЁУГөДМмПЯөҘФӘәНRFВ·ҫ¶ЎЈЧоЦХҪб№ыҫНКЗЈ¬RFFEөДөзВ·ГЬ¶ИТӘОӘФзЖЪПөНіөД4ұ¶ЎЈ

Нј10ЈәFWAМмПЯХуБРУЙөҘ¶АөДTәНRРНХуБР·ўХ№ЦБјҜіЙКҪЛ«ј«»ҜT/RРНХуБР

К№УГәБГЧІЁЖөВККұЈ¬ПаҝШХуөҘФӘЦ®јдөДёсХӨјдҫаұдөГ·ЗіЈРЎЈ¬АэИз39GHzКұОӘ3.75mmЎЈОӘЧоҙуПЮ¶ИөШјхЙЩАЎөзЛрәДЈ¬ОсұШҪ«З°¶ЛЧйјюЦГУЪҝҝҪь·шЙдөҘФӘөДО»ЦГЎЈТтҙЛЈ¬ұШРлЛхРЎRFFEөДХјУГГж»эЈ¬Н¬КұҪ«¶аЦЦ№ҰДЬХыМејҜіЙФЪВгЖ¬ЙП»т¶аРҫЖ¬ДЈҝй·вЧ°ДЪЎЈТӘФЪәЬРЎөДГж»эДЪІҝКрЛщУРХвР©№ҰДЬЈ¬РиТӘј«РЎөДPAЈ¬¶шХвҫНТӘЗуХуБРҙуРЎіЙұ¶Фцҙу»тК№УГGaNөИёЯ№ҰВКГЬ¶ИјјКхЎЈҙЛНвЈ¬ІЙУГДЬ№»ДНКЬҪПёЯҪбОВөД°лөјМејјКхЦБ№ШЦШТӘЎЈОВ¶ИёЯУЪ150ЎжКұЈ¬SiGeөДҝЙҝҝРФ»бјұҫзПВҪөЈ¬¶шGaN-on-SiCөД¶о¶ЁОВ¶ИОӘ225ЎжЎЈХвТ»75ЎжөДҪбОВУЕКЖ¶ФИИЙијЖУРәЬҙуөДУ°ПмЈ¬УИЖдКЗХл¶ФКТНвұ»¶ҜАдИҙКҪПаҝШХуЎЈ

И«КэЧЦУл»мәПХуБР

¶ФУЪBTS№©УҰЙМАҙЛөЈ¬ЧФИ»КЗТӘПИМҪЛчҪ«өұЗ°

6GHzТФПВөДИ«КэЧЦІЁКшіЙРНЎўҙу№жДЈMIMOЖҪМЁА©Х№ЦБәБГЧІЁЎЈХвСщұгҝЙТФұЈБфХл¶ФІЁКшіЙРНҝХјдёҙУГөД»щҙЎјЬ№№әНёЯј¶РЕәЕҙҰАнЛг·ЁЎЈИ»¶шЈ¬УЙУЪәБГЧІЁМṩөДРЕөАҙшҝнҙу·щМбёЯЈ¬ТФј°РиТӘРн¶аУРФҙРЕөАЈ¬ИЛГЗөЈРДҙЛАаПөНіөД№ҰәДәНіЙұҫ№эёЯТІКЗУРёщҫЭөДЎЈТтҙЛЈ¬№©УҰЙМҝӘКјМҪЛч»мәПІЁКшіЙРНјЬ№№Ј¬5ТФКөПЦ»щҙшРЕөАКэБҝУлУРФҙRFРЕөАКэБҝЦ®јдөДБй»оРФЎЈХвЦЦ·Ҫ·ЁҝЙёьәГөШЖҪәвДЈДвІЁКшіЙРНФцТжУл»щҙшҙҰАнЎЈ

КэЧЦІЁКшіЙРН

јЩЙиҪјЗшFWAІ»РиТӘК№УГҙуСцҪЗЙЁГиЈ¬ЗТЙијЖУЕБјөДБРХуМмПЯҝЙМṩёЯҙп14dBiөДФцТжЈ¬КЧПИОТГЗІЙУГТ»ёцТФ65dBm EIRPОӘДҝұкөДәБГЧІЁBTSКХ·ўЖчЙијЖЈ¬И»әуК№УГТСОККА¶аДкөДПЦіЙөг¶ФөгОўІЁОЮПЯөзЧйјю(°ьАЁёЯ№ҰВК28GHz GaNЖҪәв·ЕҙуЖч)АҙјЖЛг№ҰәДЎЈ¶аТнХуБРәНКХ·ўЖчИзНј11ЛщКҫЎЈјЩЙиК№УГСӯ»·ЖчЗТАЎөзЛрәДОӘ1.5dBЈ¬ДЗГҙМмПЯ¶ЛҝЪөД№ҰВКОӘ27dBmЎЈҙУПВКц·ҪіМҝЙТФҝҙіцЈ¬ТӘКөПЦ65dBm EIRPЈ¬РиТӘК№УГ16ёцКХ·ўЖчЈ¬ХвР©КХ·ўЖчЧйәПФЪТ»ЖрҝЙМṩ12dBөДКэЧЦІЁКшіЙРНФцТжЈә

Нј11ЈәІЙУГКэЧЦІЁКшіЙРНәНПЦіЙЙМУГЧйјюөДХуБРЙијЖ

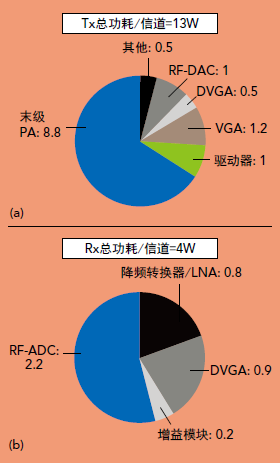

ГҝёцКХ·ўЖчөД№ҰәДИзНј12ЛщКҫЎЈ·ўЙдХјҝХұИОӘ80%КұЈ¬16ёцТнөДЧЬ№ҰәД(PDISS)ОӘГҝј«»Ҝ220WЈ¬¶шЛ«ј«»ҜПөНіФтОӘ440WЎЈ¶ФУЪРиТӘІЙУГОЮФҙАдИҙөДИ«КТНвЛю¶ҘөзЧУЙиұёЈ¬өұRFЧУПөНіөД№ҰәДі¬№э300WКұЈ¬ИИ№ЬАнҫНПаөұҫЯУРМфХҪРФБЛЎЈХвұнГчЈ¬ІЙУГөұҪсПЦіЙЧйјюөДИ«КэЧЦІЁКшіЙРНјЬ№№КЗІ»ЗРКөјКөДЎЈІ»№эЈ¬јҙҪ«ОККАөДРВРНGaN FEMҝЙ°пЦъҪвҫцХвёцОКМвЎЈИзНј13ЛщКҫЈ¬јҜіЙФЪFEMЦРөДGaN PAҪ«ҫӯ№эСйЦӨөДҝЙҝҝDohertyёЯР§МбЙэјјКхУҰУГУЪәБГЧІЁЎЈК№УГDoherty PAКұЈ¬РиТӘІЙУГКэЧЦФӨөчК§Хж(DPD)јјКхЈ»И»¶шЈ¬әБГЧІЁЖө¶ОөДБЪөА№ҰВКұИ(ACPR)ТӘЗуГчПФёьЛЙЈ¬ҙУ¶шҝЙКөПЦЎ°ёьЗбЗЙЎұөДDPDҪвҫц·Ҫ°ёЎЈPSATОӘ40dBmөД¶ФіЖРН¶ај¶Doherty PAөД№АЛг№ҰәДҝЙҪөөН50%ТФЙПЎЈФЪЙПКцПөНіЦРЈ¬өҘөҘХвТ»ПоёДҪшҫНҝЙҪ«ЧЬPDISSҪөЦБ300WТФПВЎЈјУЙПРВТ»ҙъRFІЙСщКэДЈәНДЈКэЧӘ»»ЖчКөПЦөД№ҰәДҪЪКЎЎўәБГЧІЁCMOSКХ·ўЖчөДёДҪшТФј°РЎРЕәЕјҜіЙ¶ИөДМбёЯЈ¬І»ҫГәуЈ¬ОТГЗҫНДЬДҝ¶Гёь¶аИ«КэЧЦІЁКшіЙРНҪвҫц·Ҫ°ёөДІҝКрЎЈ

Нј12Јә·ўЙд(a)әНҪУКХ(b)БҙөД№ҰәД

Нј13ЈәІЙУГ¶ФіЖРНGaN Doherty PAәНҝӘ№ШLNAөДјҜіЙКҪFEM(a)әН27.5ЦБ29.

5GHzөДPAРФДЬ(b)

»мәПІЁКшіЙРН

»мәПІЁКшіЙРНУРФҙХуБРөД»щұҫҝтНјИзНј14ЛщКҫЎЈҙЛҙҰЈ¬Nёц»щҙшРЕөАУГУЪЗэ¶ҜRFДЈДвІЁКшіЙРНЖчЈ¬Ҫш¶шҪ«РЕәЕ·ЦОӘMМхВ·ҫ¶Ј¬ІўМṩ¶АБўөДПаО»әН·щ¶ИҝШЦЖЎЈFEMУГУЪЗэ¶ҜГҝёцMөҘФӘЧУХуБРГж°еЎЈ»щҙшВ·ҫ¶әНЧУХуБРГж°еөДКэБҝУЙЛщРиҝХјдБч»тІЁКшөДЧоРЎКэБҝҫц¶ЁЎЈГҝёцЧУХуБРГж°еЦРІЁКшіЙРНЖч·ЦЦ§әНөҘФӘөДКэБҝУЙДҝұкEIRPУлG/NFИ·¶ЁЎЈҫЎ№ЬБчРРөДЙијЖұИВККЗГҝ16ЦБ64ёцУРФҙөҘФӘТ»ёц»щҙшВ·ҫ¶Ј¬ө«КөјКұИВКИЎҫцУЪІҝКріЎҫ°ЎЈАэИзЈ¬Из№ыІЙУГИИөгРЎ»щХҫ(»тФЪCPEЦХ¶ЛІа) Ј¬ ДЗГҙТ»ёц1:16өҘГж°еҫНҝЙТФБЛЎЈТ»ёцәкBTSҝЙТФУР2ЦБ4ёцЧУХуБРГж°еәН64ёцУРФҙөҘФӘЈ¬ЖдЦРГҝёцГж°еҫщОӘЛ«ј«»ҜГж°еЈ¬ТтҙЛ№ІУР4ЦБ8ёц»щҙшВ·ҫ¶әН256ЦБ512ёцУРФҙөҘФӘЎЈН¬КұАыУГКэЧЦәНДЈДвІЁКшіЙРНҝЙЧоҙуПЮ¶ИөША©ҙуёІёЗ·¶О§Ј¬»төҘ¶АПт¶аёцУГ»§МṩҝХјдЙППа»Ҙ¶АБўөДІЁКшЎЈ

Нј14ЈәІЙУГ»мәПІЁКшіЙРНөДУРФҙХуБР

УРТ»ёцЦШТӘөДОКМвҫНКЗЈ¬SiGeЗ°¶ЛКЗ·сДЬ№»МṩЧг№»өДКдіц№ҰВКәНР§ВКЈ¬ТФұЬГвК№УГёьёЯРФДЬөДIII-VЧејјКх(ИзGaA»тGaN)ЎЈАыУГіцЙ«өД·вЧ°әНјҜіЙјјКхЈ¬ХвБҪЦЦ·Ҫ·Ё¶јДЬ№»ВъЧгСПёсөДМмПЯёсХӨјдҫаТӘЗуЎЈ