机器视觉在国民经济、科学研究以及国防建设等领域都有着广泛的应用。在大批量工业生产过程中,用人工视觉检查产品质量效率低且精度不高,用机器视觉可以提高生产效率和自动化程度。图像采集系统是机器视觉系统的重要组成部分,目前图像采集常用的两种图像传感器为CCD与CMOS图像传感器。CCD一般输出带制式的模拟信号,需要经过视频解码器得到数字信号才能传入微处理器中,而CMOS图像传感器直接输出数字信号,可以直接与微处理器进行连接。不同的CMOS图像传感器有不同的性能,主要表现在图像分辨率大小不同、帧速率不同、曝光方式不同等,CMOS图像传感器可直接通过I2C来设置图像分辨率大小及曝光、增益等参数,而CCD图像传感器则需要对视频解码器进行设置来控制图像的曝光、增益等参数信息。相对于CCD图像传感器,CMOS图像传感器具有低功耗、小体积、高速数据传输和方便控制等优点,因此,CMOS图像传感器更适用于嵌入式系统应用中[1]。本文从实际应用出发,采用32位ARM9微处理器S3C2410A作为CPU来控制其他功能模块,设计实现面向机器视觉的CMOS图像采集系统,主要功能模块有SDRAM存储单元、图像采集单元、以太网传输模块、UART串口通信模块、Flash模块、电源模块等。与传统的“图像采集卡-PC-终端控制设备”模式的机器视觉系统相比,具有体积小、成本低、功耗低、实时性强、设计灵活等优点。

1 系统结构

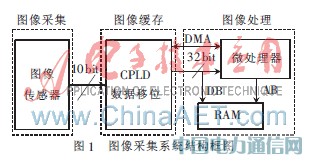

典型的机器视觉系统一般包括图像采集模块、图像数字化模块、数字图像处理模块、光源系统、智能判断决策模块和机械控制执行模块[2]。其中图像采集和数字图像处理模块的速度是评价嵌入式视觉系统硬件设计的性能指标,文献[3~6]分别给出了目前常见的四种嵌入式视觉系统结构:

(1)采用USB接口摄像头结构[3]:图像采集部分的硬件用USB接口的CMOS摄像头,摄像头应可与集成的USB的CPU接口直接相连。USB接口可以实现高速的串行通信,但USB摄像头要开发专门的驱动,大大增加了软件的开发量和难度。

(2)引入异步FIFO结构[4]:在图像传感器和主控CPU间采用异步FIFO解决传感器输出数据频率和主控CPU采集频率不匹配的问题,当FIFO满时CPU再快速读取FIFO数据。异步FIFO可以是双口RAM或者在FPGA内开辟。

(3)CPLD为核心的图像采集结构[5]:直接由CPLD根据图像传感器输出的时序信号,控制SRAM的读写,当一帧数据信息采集完毕后向CPU发送采集完毕信号;CPU需要对图像进行处理时,再通过CPLD到SRAM里读取数据。

(4)由外部中断实现图像采集结构[6]:图像传感器的帧同步、行同步和像元同步信号分别与CPU的一个外部中断连接,CPU根据中断次数来判断一帧图像是否采集完成。

通过对几种方案的对比分析,综合实际应用及开发难度等因素,确定系统结构如图1所示,系统由图像采集、图像缓冲和图像处理三部分组成。在图像缓存中,CPLD将图像传感器采集的10位数据移位成32位,再通过外部请求DMA的办法,由主控CPU的DMA控制器将32位数据送到RAM保存。这样可以减少常见中低速图像采集的资源浪费,又避免了CPU响应滞后的缺点。

2 硬件设计

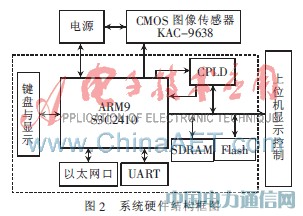

系统总体硬件结构图如图2所示。其中,图像采集器采用柯达公司的CMOS单色图像传感器KAC9638;图像的缓存由CPLD芯片XC95144和外扩SDRM(HY57V561620)组成;图像处理核心部分采用Samsung公司的ARM9(S3C2410A),并外扩了UART、以太网通信接口、USB口及LCD人机接口,方便系统调试和与其他设备交换数据。

硬件系统工作流程是:(1)系统上电后ARM9通过I2C接口直接对图像传感器进行初始化,然后等待上位机命令;(2)接收到上位机命令后,ARM9先进行DMA初始化,然后向CPLD发送采集命令。CPLD启动图像采集并申请ARM9的DMA,将一帧图像的数据保存到ARM9的SDRAM中;(3)完成图像采集后ARM9进入DMA完成,进行图像处理并将结果通过串口输出。

2.1 存储器选择

S3C2410A芯片外部可寻址的存储空间是1 GB,被分成8个存储块,每块128 MB,各个存储块由片选信号nGCS0~nGCS7译码产生。数据总线引脚为DATA0~DATA31共32根,可配置成8 bit/16 bit/32 bit的数据宽度;地址总线引脚为ADDR0~ADDR26共27根,支持128 MB空间。S3C2410A是32位的微处理器,外部总线也是32位,要充分发挥其32位总线性能优势,应采用32位的存储系统。方法是采用两片16位数据宽度的Flash存储器芯片并联或一片32位数据宽度的Flash存储器芯片。本设计采用了两片Intel的E28F128J3A组成了16M×32bit的NOR Flash,其中一片为高16位,另一片为低16位。采用三星公司的两片半字SDRAM (HY57V561620)共同组成一个16 M×32 bit的SDRAM系统,提高了其与CPU的通信效率。

2.2 通信接口设计

2.2.1 UART及USB接口设计

S3C2410A的UART提供了三个独立的异步串行I/O口,每个串行口可以独立地工作在中断模式和DMA模式。UART使用系统时钟,支持最高230.4 kb/s波特率的数据通信。每个UART串行口提供两个16 B的FIFO分别用来做发送和接收缓冲。本系统采用MAX202芯片作为RS-232的接收器/驱动器,将UART0和UART1连接到9DB接头与DSP和PC通信。S3C2410A有2个USB主设备和1个USB从设备,USB设备控制器允许DMA模式的批量传输、中断传输和控制传输。在系统设计中,USB设备用来和PC机通信供调试用,因此使用从设备口(兼容USB Ver1.1标准)。

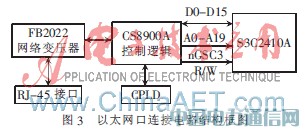

2.2.2 以太网接口电路设计

S3C2410A片上没有以太网口,因此必须外加以太网控制器才能扩展。系统采用16位以太网控制器CS8900A,该芯片的特点是:符合IEEE802.3标准,支持全双工收发可达10 Mb/s,内置SRAM收发缓冲,减轻了对主处理器的开销。以太网电路如图3所示,S3C2410A通过16位数据线,20位地址线连接CA8900A。片选信号为nGCS3,即将CS8900A的内部寄存器和帧缓冲区映射到S3C2410A的Band4中连续4 KB的存储区中,主机可以通过这个存储空间直接访问CS8900A的内部寄存器和帧缓冲区。CS8900A与RJ-45接口直接连接一个网络变压器,起到电平转换及电气隔离的作用。此外,CS8900A提供两种操作模式:I/O模式和内存模式,本系统通过CPLD选择其工作模式。

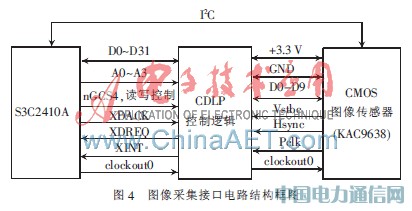

2.3 图像采集模块电路设计

图像传感器采用柯达公司生产的CMOS单色图像传感器KAC9638。KAC9638是高性能、低功耗、SXGA CMOS有源像元传感器,具有以下特点:(1)KAC9638是1/2英寸,1 024×1 280有效图像阵列的CMOS图像传感器,在满足应用场合所需的分辨率条件下,还具有良好的动态范围(55 dB),最小照度(2.40/Lux-sec)等性能;(2)KAC9638内置10位的A/D转换器,直接输出8位或10位的数字灰度值,在保证精度的同时不需另外接A/D转换器,大大简化外围电路;(3)KAC9638具有良好的电源管理功能和低功耗特性。数据传送时芯片的总功耗为150 mW。此外,为进一步降低系统的功耗,芯片还具有可编程“上电”和“下电”模式。CMOS图像传感器目前普遍采用I2C总线,本系统通过S3C2410A的I2C总线与KAC9638的SCL、SDA连接。由S3C2410A直接完成对图像传感器的初始化。KAC9638内部嵌入了一个10位A/D转换器,因而可以同步输出10位的数字视频流,但是S3C2410A具有32位的外部总线,直接将10位数据接到总线上会造成资源浪费,降低CPU效率,因此,KAC9638和S3C2410A之间连接CPLD,由CPLD完成10位视频数据到32位的转换,图像采集接口电路结构框图如图4所示。

为使S3C2410A能像访问内存一样读取图像传感器的数据,将CPLD映射到S3C2410A的存储单元上。CPLD上的图像缓存片选信号nGCS4,地址映射到S3C2410A的Bank4,地址范围:0x20000000~0x27ffffff。实际只用其中的一个地址0x20000000(即DMA的源地址)。图像传感器由S3C2410A的clockout0引脚提供。此外,PCLK、HREF、VSYNC分别为像素、行、帧同步信号;OE为图像传感器启动采集信号;XINT是ARM9与CPLD的外部中断联络信号;XDREQ和XDACK为S3C2410A的DMA的请求和握手信号。

3 系统驱动软件设计

3.1 I2C串行总线通信协议

I2C总线是嵌入式系统常见的网络接口,由SCL(串行时钟)和SDA(串行数据)两根总线构成。该总线有严格的时序要求,总线工作时,由串行时钟线SCL传送时钟脉冲,由串行数据线SDA传送数据。总线必须由主设备控制,主设备产生串行时钟控制总线的传输方向,并产生起始和停止条件。I2C总线传输一个字节的时序如图5所示。当主设备写从设备时,传输的数据要跟有从设备的地址。从设备不能主动执行数据传输,所以主控设备读从设备时必须发送一个带有从设备地址的读请求。本系统中ARM9是主设备,图像传感器是从设备,ARM9通过I2C总线改写KAC9638寄存器的值完成初始化。根据I2C通信协议,改变某个寄存器的值的过程是:先发送CMOS传感器特定写地址(7位地址+0),紧接着发送需要写的寄存器的地址,再发送数据;而要读取某个寄存器的值的过程是:先发送CMOS传感器特定写地址,紧接着发送需要读的寄存器的地址,再发送CMOS传感器特定读地址(7位地址+1),最后接收数据。

3.2 图像采集CPLD时序控制

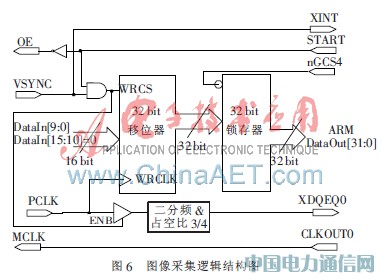

CPLD采集两个10位像元数据组合成32位(不够的位用0补充)可以提高图像采集效率。并且设计中使用DMA的方式保存图像数据,可以减少CPU的开销。以CPLD为核心器件设计的图像采集逻辑结构图如图6所示。

逻辑结构图的工作原理如下:

(1)CLKOUT0为S3C2410A的输出时钟引脚,根据S3C2410A内部寄存器MisCCR中4~6位的不同设置可以输出不同的时钟,如系统时钟FCLK、AHB(内部)总线时钟HCLK和APB(外部)总线时钟PCLK等。系统将其作为CMOS图像传感器的主时钟输入MCLK。

(2)启动信号START为S3C2410A的一个I/O,高电平有效,由于KAC9638的启动信号OE是低电平有效,所以它们之间要连接一个非门。

(3)VSYNC为传感器的帧同步信号,输出一帧有效图像时该信号一直为高电平,用该信号连接S3C2410A的外部中断XINT,使CPU能控制一帧图像的开始和结束。

(4)D[9:0]为图像传感器输出的数据流,D[15:10]位用0填充,组成16位数据输入到缓冲。缓冲的写入允许信号是启动信号START和帧有效信号VSYNC的逻辑与。在缓冲内两个周期移位成32位数据。

(5)缓冲写入时钟WRCLK由传感器的像元输出时钟PCLK提高,一个周期写入一个10位A/D值,所以一次输出32位数据时,输出时钟周期是PCLK的二分频。并将PCLK的二分频作为S3C2410A外部DMA的请求信号XDREQ。

(6)片选信号线nGCS4:作为32位缓冲的控制线,低电平有效。在进行数据采集时将DMA方式的源地址设置在BANK4范围内,读操作时即选中该缓冲。

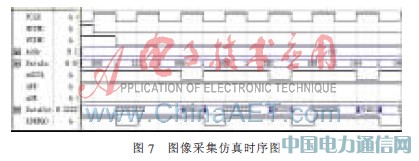

图7是用Verilog语言编写的程序仿真的图像采集时序图。

3.3 DMA方式采集图像数据程序设计

系统采集一帧图像数据的流程图如图8所示。

(1)启动图像采集:主控CPU从串口或其他通信口接收到采集命令后,通过START信号线通知CPLD采集信号,CPLD再通过硬件引脚OE启动KAC9638采集图像数据。

(2)DMA初始化:包括DMA的源地址、目标地址、DMA次数等初始化。

(3)开外中断:当一帧数据采集完成后,通过外部中断通知CPU。

(4)DMA数据传输无需CPU干预,一帧图像完成后产生中断。

(5)DMA中断产生并且外部中断产生才算是一帧图像采集完成,然后交由主控CPU进行处理。若只有其中一个中断产生,并且等待另一个中断超时,则是在采集过程中丢失了数据,采集图像失败。

4 硬件调试

4.1 硬件调试环境

在系统硬件调试中,使用集成开发环境配合JATG仿真器进行调试是目前采用最多的一种调试方式[7]。集成开发环境选用ARM公司的ADS1.2。JTAG仿真器也称为JTAG调试器,是通过ARM芯片的JATG边界扫描口进行调试的设备。属于完全非插入式(即不使用片上资源)调试。

4.2 硬件调试步骤及结果

(1)BootLoad系统引导测试

先使用英蓓特公司开发的Flash烧写工具将BootLoad程序烧写到Flash,若在PC超级终端上能正确接收目标板的串口返回的启动信息,表明系统正常运行,可以用ADS下载程序到SDRAM进行调试。

(2)图像传感器测试

①I2C配置测试

将ADS编译好的bin文件下载到目标板的SDRAM,超级终端接收到返回的图像传感器ID正确,则表明I2C通信正常。通过I2C配置图像大小为3(H)×5(V),用示波器测量传感器帧同步(vsync)、行同步(hsync)及像元时钟(pclk)的关系。如图9所示,11个像元时钟(设定的每行3个像元加上每行开始的8个全黑像元)对应1个行同步时钟,图10显示了帧同步信号及行同步信号的关系:5个行同步时钟对应1个帧同步时钟。测试结果表明S3C2410A可以正确配置图像传感器的工作方式。

②图像采集测试

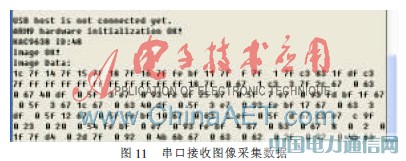

为方便检验采集到的图像,将ARM采集到的图像数据通过UART口发送到PC终端,再将数据组合成图像显示。接收到的数据如图11所示。

采用CMOS图像传感器、CPLD和ARM9的DMA结合完成图像的采集是本系统的特点。该方法提高了图像的采集速度,减少了CPU的开销。CMOS图像传感器价格适中,外围简单,且集成I2C接口便于编程控制;CPLD将CMOS传感器输出数据移位成32位数据,可以使传感器以更高的速度输出;ARM9的DMA负责图像采集,使得CPU可以解放出来处理其他任务。实验测试结果证明,该图像采集系统硬件平台方案设计合理、可行。该系统在实际中可以应用于视频图像监控、图像自动检测、医疗及军事检测等场所,具有良好的应用前景。

参考文献

[1] 李继军,杜云刚,张丽华等.CMOS图像传感器的研究进展[J].激光与光电子学进展,2009(04):45-52.

[2] 付斌,王科俊,陆扬.基于USB2.0的CMOS图像采集系统的实现[J].微计算机信息,2009(10):96-98.

[3] 李洪宇.机器视觉图像采集设计与研究[D].大庆:大庆石油学院,2007.

[4] 龙再川,赵凯生,洪明坚,等.ARM系统中DMA方式在数据采集中的应用[J].国外电子元器件,2007(2):66-69.

[5] 林志琦,张修谦,富丽,等.基于TMS320F2812和CPLD的200万像素数字图像采集系统接口的设计[J].长春理工大学学报,2007,30(2):39-41.

[6] 叶权来,郑黎明.ARM9平台下的CMOS图像传感器数据采集系统[J].电子工程师,2007,33(6):70-72.

[7] 符意德,陆阳.嵌入式系统原理及接口技术.北京:清华大学出版社,2007.