ХӘТӘЈәІЙУГБҪЖ¬TI№«ЛҫөДЧЁУГКУЖөҙҰАнРҫЖ¬TMS320DM642ЙијЖБЛТ»ЦЦ¶аВ·КУЖөјаҝШПөНіЎЈЖдЦРЈ¬DSP1УлКУЖөІЙјҜРҫЖ¬SAA7113№ІН¬НкіЙ¶аВ·КУЖөөДІЙјҜЈ¬ІўЖҙҪУіЙТ»В·КУЖөНјПсКдіцЈ»DSP2НкіЙ¶ФDSP1КдіцНјПсөДІЙјҜЎўС№ЛхәНКУЖөҙ«КдЎЈёГ·Ҫ°ёҪб№№Бй»оЎўНШХ№РФЗҝЈ¬ҝЙТФКөПЦ4В·КУЖөөДКөКұІЙјҜУлҙ«ЛНЎЈ

ТэСФ

ФЪёЦМъТұБ¶јУ№ӨөИёЯОВёЯОЈРРТөЦРЈ¬УРРн¶аіЎәПІ»ККәП№ӨИЛіӨКұјдФЪПЦіЎјаҝШЙиұёФЛРРЈ¬ТтҙЛРиТӘФЪПЦіЎҪЁБўёфАл№ӨЧчКТЈ¬АыУГКУЖөјаҝШПөНіҪ«ПЦіЎөДКөКұКУЖөІЙјҜәНҙ«КдЦБ№ӨЧчКТЦРЎЈОӘБЛКөПЦИ«·ҪО»өДЙиұёјаҝШЈ¬НщНщРиТӘ¶аВ·КУЖөјаҝШПөНіЈ¬ұҫОДХл¶ФКөјКЗйҝцЈ¬ІЙУГTI№«ЛҫөДЧЁУГКУЖөҙҰАнРҫЖ¬TMS320DM642№№ҪЁөҘ°е¶аВ·КУЖөјаҝШПөНіЎЈёГПөНіБ¬ҪУјтөҘЎў·ҪұгЈ¬ЙиұёіЙұҫөНЈ¬ҝЙТФ№г·әУҰУГУЪПЦіЎјаҝШПөНіЦРЎЈ

1 әЛРДҙҰАнЖчСЎФс

КУЖөПөНіНЁіЈ°ьАЁКУЖөРЕәЕөДІЙјҜЎўҙҰАнәНКдіцЎЈЖдЦРЧоәЛРДөДІҝ·ЦКЗҙҰАнІҝ·ЦЎЈ¶ФУЪ4В·720×576ұкЗеёсКҪөДPALЦЖКҪКУЖөІЙјҜПөНіј°1В·720×576ұкЗеёсКҪөДPALЦЖКҪКУЖөКдіцЈ¬ПөНіКдИлөДКэҫЭБҝОӘЈә

ЈЁ720×576Ј© ×4×16 bit×25 Hz≈79.1 MB/s

КдіцКэҫЭБҝОӘЈә

ЈЁ720×576Ј©×16 bit×25 Hz≈19.8 MB/s

ҙҰАнИзҙЛҫЮҙуөДКэҫЭБҝіЙОӘ¶аВ·КУЖөјаҝШПөНіөДЧоҙуЖҝҫұЎЈХвТӘЗуDSPУРЧг№»іцЙ«өДНвІҝҪУҝЪДЬБҰәНҪПёЯөДДЪәЛКұЦУЈ¬К№УГёЯЛЩөД»әіеЙиұёәНёЯЛЩөДҙжҙўЖчЈ¬ІўІЙУГёчЦЦјјКхНкіЙі¬ҙуБҝКУЖөКэҫЭөДІЙјҜәНҙҰАн[8]ЎЈ

TMS320DM642ЈЁјтіЖDM642Ј©КЗTI№«ЛҫНЖіцөДЧЁУГКУЖөҙҰАнРҫЖ¬ЎЈЖд»щУЪC64XДЪәЛЈ¬ІЙУГVLIWЈЁі¬іӨЦёБоЧЦЈ©Ҫб№№әН¶юј¶»әҙжҪб№№Ј»ЧоёЯЦчЖөКұЦУҙп720 MHzЈ¬УөУР·бё»өДНвЙиҪУҝЪЈәУөУР3ёцҝЙЕдЦГКУЖөҝЪЈ¬ҝЙКөПЦУлКУЖөКдИл/КдіцөДОЮ·мБ¬ҪУЈ»УөУР64В·ҝЙЕдЦГEDMAЈ¬ҝЙТФБй»оөШКөПЦКэҫЭөД°бТЖІЩЧчЈ»ҫЯУР64О»НвІҝҙжҙўЖчҪУҝЪЈЁEMIFAЈ©Ј¬ҝЙТФБ¬ҪУН¬ІҪ»тХЯТмІҪөДҙжҙўЖчәННвЙиЈ»УөУРI2CЧЬПЯҪУҝЪЈ¬ҝЙКөПЦ¶ФНвІҝұаҪвВлРҫЖ¬өДЕдЦГ[1]ЎЈ

DM642УөУР3ёцҝЙЕдЦГөДКУЖөҝЪНвЙиЈЁVP0Ј¬VP1Ј¬VP2Ј©ЎЈГҝёцКУЖөҝЪҫЯУРБҪёцНЁөАЈ¬ГҝёцНЁөА¶јҝЙТФКөПЦУлНЁУГКУЖөұаВлЖчәНҪвВлЖчОЮ·мБҙҪУЈ¬Ц§іЦCCIRӘІ601ЎўITUӘІBT.656ЎўBT.1120өИКУЖөұкЧјЎЈХвСщГҝёцDSPҝЙТФЕдЦГ2ёцКУЖөУГУЪКУЖөІЙјҜЈЁјҙН¬КұІЙјҜ4ёцНЁөАЈ©Ј¬БнТ»ёцКУЖөҝЪУГУЪКдіцПФКҫЎЈБнНвЈ¬DM642»№УөУРТ»ёц10/100MТФМ«НшҪУҝЪЈ¬ҝЙТФКөПЦУлНвІҝНшВзөДБ¬ҪУЎЈТтҙЛ,ІЙУГDM642ЧчОӘЦчҙҰАнРҫЖ¬АҙКөПЦКУЖөөДІЙјҜЎўС№ЛхУлҙ«КдөИ№ҰДЬЎЈҝјВЗөҪПөНіІ»ҪцРиТӘІЙјҜ¶аВ·ұкЗеPALЦЖКҪКУЖөЈ¬»№РиТӘҪшРРH.264С№ЛхұаВлЈ¬әЬДСАыУГөҘDSPПөНіАҙҙпөҪКөКұРФТӘЗуЈ¬ТтҙЛІЙУГБЛЛ«DSPПөНіЎЈЖдЦРТ»ёцDSPёәФрІЙјҜУлЖҙҪУЈ¬БнТ»ёцDSPёәФрКУЖөС№ЛхУлҙ«ЛНЎЈ

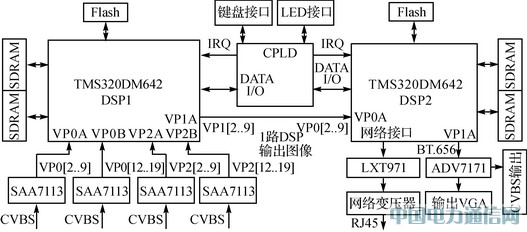

2 ПөНіЧЬМеЙијЖ

ПөНіІЙУГDM642ОӘПөНіәЛРДРҫЖ¬Ј¬АыУГDM642өДКУЖөҝЪ»ҘБ¬јјКхКөПЦDSPјдөДНЁРЕ[5]ЎЈФЪКУЖөІЙјҜ¶ЛЈ¬УЙDSP1әН4ёцSAA7113№№іЙ4В·КУЖөІЙјҜПөНіЈ¬DSP1өДКУЖөКдіцҝЪҪУDSP2өДКУЖөІЙјҜКдИлҝЪЎЈDSP2ФЪПөНіЦРЦчТӘКөПЦH.264С№ЛхұаВл№ҰДЬЈ¬С№ЛхәуөДКэҫЭНЁ№эНшВзҪУҝЪЛНЦБЧЬјаҝШКТЈ»БнНвЈ¬DSP2өДКУЖөҝЪ2НвҪУКУЖөұаВлРҫЖ¬Ј¬НкіЙДЈДвCVBSј°RGBёсКҪКУЖөКэҫЭөДКдіцЎЈПөНіҪб№№ҝтНјИзНј1ЛщКҫЎЈ

Нј1 ПөНіҪб№№ҝтНј

3 ПөНіУІјюЙијЖ

3.1 КУЖөҪвВлДЈҝйЙијЖ

КУЖөҪвВлДЈҝйТІіЖОӘКУЖөІЙјҜДЈҝйЈ¬ЛьУЙКэЧЦКУЖөҪвВлРҫЖ¬SAA7113[4]әНКУЖөФҙЈЁДЈДвCVBSРЕәЕЈ©ЧйіЙЎЈКдИлөДНјПсҫӯ№эКУЖөҪвВлДЈҝйҪшРРA/DЧӘ»»әуЈ¬ІЕДЬЛНёшКУЖөҙҰАнДЈҝйЎЈёГҪвВлДЈҝйІЙУГPhilips№«ЛҫөДSAA7113РҫЖ¬АҙҪшРРІЙјҜЎЈНјПсҙ«ёРЖчКдіцөДДЈДвCVBSРЕәЕҫӯSAA7113КУЖөРҫЖ¬ЧӘ»»ОӘКэЧЦРЕәЕЈ¬КдіцөДКэЧЦРЕәЕҫӯ№эDM642КУЖөҝЪөДДЪІҝFIFO»әіеәуЈ¬УЙDM642өДEDMAНЁөАҪ«КэҫЭҙ«ЛНөҪЖ¬НвSDRAMЦРЈ¬ТФұгКУЖөҙҰАніМРтК№УГЎЈDM642НЁ№эI2CҝШЦЖЖч¶ФSAA7113ҪшРРЕдЦГЈ¬К№ЖдКдіцBT.656ёсКҪ4ЎГ2ЎГ2өДYUVКУЖөКэҫЭБчЎЈ

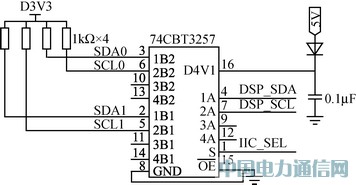

ХвАпРиТӘЛөГчөДКЗЈ¬УЙУЪDM642Ц»УРТ»ёцI2CҪУҝЪЈ¬Чо¶аЦ»ДЬС°Ц·БҪёцI2CҙУЙиұёЎЈОӘБЛКөПЦDM642¶Ф4ёцКУЖөҪвВлРҫЖ¬өДЕдЦГЈ¬К№УГТ»ёц¶аВ·СЎФсҝӘ№Ш74CBT3257Ҫ«I2CЧЬПЯ·ЦіЙI2C0әНI2C1ЎЈI2CЧЬПЯЗР»»өзВ·ИзНј2ЛщКҫЎЈ

Нј2 I2CЧЬПЯЗР»»өзВ·

3.2 Л«DSPНЁРЕЙијЖ

КөПЦЛ«DM642өДНЁРЕЙијЖҝЙТФІЙУГБҪЦЦ·ҪКҪЈәЛ«¶ЛҝЪRAMәНКУЖөҝЪ»ҘБ¬ЎЈЛ«¶ЛҝЪRAMІЙУГ№ІПнДЪҙжөДДЈКҪЈ¬ПөНіКұРтёҙФУЈ¬ҝмЛЩЛ«¶ЛҝЪRAMөДіЙұҫҙъјЫёЯЈ¬ТтҙЛФЪұҫПөНіЦРІЙУГКУЖөҝЪ»ҘБ¬јјКхКөПЦЛ«DSPөДНЁРЕЙијЖЎЈ

ІЙУГКУЖөҝЪ»ҘБ¬јјКхөДУЕөгУРЈә

ўЩ өзВ·ЙијЖјтөҘЈ¬КөПЦПөНіНЁРЕЦ»РиТӘ13ёщРЕәЕПЯЈ¬°ьАЁ8ёщКУЖөҝЪКэҫЭПЯЎў2ёщКұЦУПЯј°3ёщҝЙСЎөДҝШЦЖРЕәЕПЯЈЁРРіЎН¬ІҪРЕәЕЈ©ЎЈ

ўЪ DM642өДКУЖөЦ§іЦBT.656ёсКҪКУЖөКдіцЈ¬¶шBT.656ёсКҪКэЧЦКУЖөҪ«Н¬ІҪРЕәЕДЪЗ¶ФЪКэҫЭБчЦРЈ¬ТтҙЛОЮРиРРіЎН¬ІҪРЕәЕЈ¬јҙОЮРиЖдЛыРҫЖ¬ёЁЦъҝШЦЖЎЈ

ўЫ ҙ«КдЛЩВКёЯЈ¬ҝЙҙп80 MB/sЎЈ

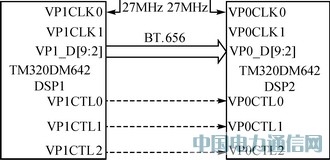

Л«DSPНЁРЕДЈҝйөДЙијЖИзНј3ЛщКҫЎЈПөНіЦ»РиҪ«DSP1өДКУЖөҝЪ1ЕдЦГіЙПФКҫДЈКҪЈ¬ФтVP1AҪ«Кдіц·ыәПBT.656ёсКҪөДКэЧЦКУЖөКэҫЭБчЈ»Н¬КұҪ«DSP2өДКУЖөҝЪ0ЕдЦГіЙІЙјҜДЈКҪЈ¬ІЙјҜDSP1КдіцөДBT.656КэЧЦКУЖөБчЈ¬И»әуҪшРРҪвёфРРј°H.264С№ЛхҙҰАнЎЈУЙУЪBT.656КэЧЦКУЖөБчДЪЗ¶УРН¬ІҪРЕәЕЈ¬ТтҙЛVPxCTL[0:2]ҝЙҪУҝЙІ»ҪУЎЈ

Нј3 Л«DSPНЁРЕЙијЖ

3.3 НшВзҪУҝЪДЈҝйЙијЖ

НшВзҪУҝЪДЈҝйЦчТӘУЙDM642ТФМ«НшҪУҝЪЎўНшВзОпАнІгРҫЖ¬LXT971ј°НшВзұдС№ЖчЧйіЙЈ¬ЖдЦчТӘ№ҰДЬКЗҪ«ҫӯDSP2С№ЛхұаВләуөДH.264КУЖөКэҫЭБчҙ«КдөҪЧЬјаҝШКТЦРЎЈLXT971КЗ10/100BaseӘІTXТФМ«НшҝШЦЖЖчЈ¬јжИЭIEEE802.3ұкЧјЈ¬МṩMIIҪУҝЪЈ¬ҝЙКөПЦУлDM642өДMIIҪУҝЪОЮ·мБ¬ҪУЎЈПөНіЦРөДНшВзұдС№ЖчІЙУГ1:1өДHR601680Ј¬ЖдЦчТӘЧчУГКЗЖҘЕдЧиҝ№ЎўФцЗҝРЕәЕЎўМбёЯҙ«КдҫаАлТФј°КөПЦөзС№ёфАлЎЈУЙУЪLXT971РҫЖ¬өДUTP¶ЛҝЪОӘөзБчРНЗэ¶ҜЈ¬ТтҙЛНшВзұдС№ЖчөДЦРјдійН·УҰҪУөзИЭөҪөШ¶ЛЎЈҙУDM642ҙ«КдАҙөДКэҫЭҫӯLXT971ЧӘ»»ОӘТФМ«НшОпАнІгДЬҪУКХөДКэҫЭәуЈ¬ҫӯУЙНшВзұдС№ЖчНЁ№эRJӘІ45ҪУҝЪҙ«КдөҪТФМ«НшЎЈ

3.4 КУЖөұаВлДЈҝйЙијЖ

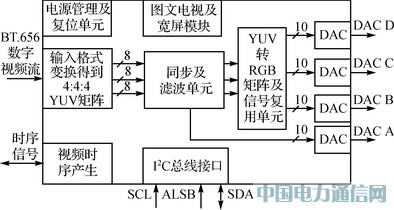

КУЖөұаВлДЈҝйТІіЖОӘКУЖөПФКҫДЈҝйЎЈІЙУГADV7171КөПЦКУЖөұаВл№ҰДЬЈ¬өГөҪТ»В·CVBSј°Т»В·VGAДЈДвКУЖөКдіцЎЈADV7171КЗADI№«ЛҫЙъІъөДКУЖөұаВлЖчЈ¬ҝЙҪ«·ыәПBT.656ј°BT.601ёсКҪөДКэЧЦКУЖөЧӘ»»іЙCVBSёҙәПКУЖөРЕәЕЎўДЈДвRGBРЕәЕ»тХЯSVideoРЕәЕКдіцЈ¬Н¬КұЦ§іЦөзКУЧЦД»ј°НјОДөзКУЎЈЖд№ҰДЬҝтНјИзНј4ЛщКҫЎЈDM642өДVP1AКдіцBT.656КэЧЦКУЖөБчЦБADV7171Ј¬ADV7171НкіЙұаВлј°ёсКҪЧӘ»»№ҰДЬәуН¬КұКдіцТ»В·CVBSРЕәЕј°Т»В·RGBРЕәЕЈ»Н¬КұЈ¬АыУГDM642өДI2CҪУҝЪНкіЙADV7171өДЕдЦГЎЈ

Нј4 ADV7171№ҰДЬҝтНј

3.5 ҙжҙўҝХјдА©Х№

DM642ІЙУГҙжҙўУіЙдөД·ҪКҪАҙЧйЦҜҙжҙўҝХјдЈ¬ЖдЦР¶юј¶»әҙжУіЙдФЪ0x00000000~0x0003FFFFЈЁ№І256 KBЈ©Ј¬НвІҝҙжҙўЖчҝХјдУіЙдФЪ0x80000000ТФәуөДөШЦ·ҝХјдЦРЎЈНвІҝҙжҙўҝХјдУЦ·ЦОӘ4ёцҝЙ¶АБўС°Ц·өДҝХјдCE0Ў«CE3Ј¬ЧФөШЦ·0x80000000ЖдёчХј256 MBЈ¬ГҝёцҙжҙўҝХјд¶ФУҰТ»ёцCEҝХјдҝШЦЖјДҙжЖчЈ¬НЁ№эјДҙжЖчЙиЦГГҝТ»ёцҝХјдөДҙжҙўЖчАаРНЎЈ

DM642НЁ№эEMIFЈЁExternal Memory InterfaceЈ©[2]ҙжҙўЖчҪУҝЪ·ГОКЖ¬НвҙжҙўЖчЈ¬ЛьјҜіЙБЛКэЧйЧЬПЯЎўөШЦ·ЧЬПЯЎўТмІҪҝШЦЖЧЬПЯј°SDRAMЎўSBSRAMҝШЦЖЧЬПЯЈ¬Ц§іЦSDRAMЎўSBSRAMЎўFlashөИҙжҙўЖчОЮ·мҪУҝЪЙијЖЎЈҪ«CE0ҝХјдЕдЦГіЙ64О»ҝн¶ИЈ¬Ц»УГУЪSDRAMДЪҙжөДУіЙдЈ»CE1ҝХјдЕдЦГіЙ8О»КэҫЭҝн¶ИЈ¬УГУЪFlashҙжҙўҝХјдА©Х№Ј»CE2ЎўCE3ұҫЙијЖЦРОҙК№УГЈ¬БфЧчҪ«АҙА©Х№К№УГЎЈ

3.5.1 SDRAMҪУҝЪ

DM642өДEMIFҪУҝЪУөУРSDRAMҝШЦЖЖчҪУҝЪЈ¬ҝЙТФКөПЦУлSDRAMРҫЖ¬өДОЮ·мБ¬ҪУЎЈҪ«CE0ЧУҝХјдЕдЦГОӘ64О»өДSDRAMҪУҝЪЈ¬Ҫ«БҪЖ¬4M×32О»өДSDRAMНШХ№іЙ4M×64О»Ј¬ФЪCE0ЧУҝХјдөДҫЯМеөШЦ·¶ЁО»ОӘ0x80000000Ў«0x81FFFFFFЎЈSDRAMІЙУГHynix№«ЛҫөДHY57V283220РҫЖ¬ЎЈЛьҫЯУР4ёцОпАнBankЈ¬ГҝёцBankөДҝХјдОӘ1M×32О»Ј¬ЛўРВЦЬЖЪОӘ64 msЈ¬ҝЙТФБ¬Рш»тХЯҪ»ҙнН»·ў¶БРҙ1Ўў2Ўў4Ўў8»тХыТіКэҫЭЎЈSDRAMөД№ӨЧчКұЦУУЙDSPөДECLKOUT1МṩЈ¬ҝЙУЙAEA19әНAEA20ТэҪЕЕдЦГОӘEMIFөДCPUКұЦУөД1/4»т1/6ЎЈSDRAMЦчТӘУГАҙҙжҙўҙуБҝөДНјПсКэҫЭЎЈГҝЖ¬DSPРиТӘ2Ж¬SDRAMЈ¬2Ж¬DSPҫНРиТӘ4Ж¬SDRAMЎЈSDRAMА©Х№ФӯАнНјВФұаХЯЧўЎЈ

3.5.2 FlashҪУҝЪ

DM642өДНвІҝҙжҙўЖчҪУҝЪ»№МṩБЛТмІҪҪУҝЪЈ¬УГУЪУл¶аЦЦҙжҙўЖчәНҝЙұаіМНвІҝЙиұёҪУҝЪЈ¬ИзSDRAMЎўE2PROMәНFlashҙжҙўЖчЈ¬Н¬КұТІ°ьАЁFPGAЎўCPLDөИЎЈПөНіОӘГҝёцDSP¶јЕдЦГБЛТ»Ж¬4M×8О»өДFlashЈ¬УГУЪ№М»ҜіМРтәНіхКј»ҜКэҫЭЎЈПөНіЙПөз»тХЯёҙО»әуЈ¬ҙУFlashөД0x00000000ҙҰҝӘКјјУФШіМРтәНКэҫЭөҪSDRAMҝХјдЎЈDSPҪ«EMIFөДCE0ЧУҝХјдЕдЦГОӘ8О»ТмІҪҫІМ¬ҙжҙўЖчFlashҪУҝЪЎЈFlashСЎУГ90 nsөДAM29LV320DTЈ¬УөУР22ёщөШЦ·ПЯЎЈУЙУЪDM642өДНвІҝөШЦ·ЧЬПЯЦ»УРA[22Јә3]Ј¬ЛщТФCE0ЧУҝХјдөДЧоҙуС°Ц··¶О§ОӘ1M×8О»ЎЈCE1ЧУҝХјдіэБЛ·ЦЕдёшFlashҝХјдНвЈ¬»№·ЦЕдёшЧҙМ¬/ҝШЦЖјДҙжЖчөИЧКФҙК№УГЈ¬FlashЦ»ХјҫЭCE1ЧУҝХјдөДТ»°лС°Ц·ҝХјдЈ¬ЧоҙуҝЙС°Ц··¶О§ОӘ512K×8О»Ј¬¶шFlashөДЙијЖИЭБҝОӘ4M×8О»ЎЈОӘБЛ·ГОКХыёцFlashҝХјдЈ¬РиҪ«FlashҪшРР·ЦТіЈ¬ГҝТіОӘ512 KBЈ¬№І·Ц8ТіЈ¬ТіөШЦ·PA20ЎўPA19ЎўPA18ј°FlashЖ¬СЎРЕәЕ¶јКЗАҙЧФCPLD[8]ЎЈFlashҪУҝЪөзВ·ВФ——ұаХЯЧўЎЈ

4 PCBөзВ·ЙијЖ

DM642өДДЪәЛКұЦУҙпөҪ720 MHzЈ¬SDRAMЧЬПЯЛЩ¶ИҙпөҪ133 MHzЈ¬ПөНіКфУЪёЯЛЩРЕәЕөзВ·ЎЈОӘБЛұЈЦӨПөНіХэіЈ№ӨЧчЈ¬РиТӘҝјВЗҙ«КдПЯР§УҰЎўРЕәЕНкХыРФЎўөзФҙНкХыРФј°өзҙЕјжИЭРФөИОКМвЈ¬АыУГёЯЛЩөзВ·ІјПЯЦӘК¶ЙијЖЧиҝ№ЖҘЕдј°ІгөюҪб№№Ј¬ІўұЈЦӨБјәГөД№©өзПөНіЎЈ

КЧПИЈ¬Т»ёцБјәГөДөюІгЙијЖКЗұЈЦӨПөНіөДРЕәЕНкХыРФј°өзФҙНкХыРФөД№ШјьЈ¬Н¬КұБјәГөДөюІгҪб№№ЙијЖТІУРЦъУЪөзВ·өДІјНЁЎЈұҫПөНіЦРІЙУГ8ІгөзВ·Ҫб№№Ј¬Хв8Іг°е·ЦІгҪб№№ОӘРЕәЕІг1—өШІг—РЕәЕІг2—өзФҙІг—өШІг—РЕәЕІг3—өШІг—РЕәЕІг4Ј¬ЖдЦРРЕәЕІг1әНРЕәЕІг4·ЦұрОӘTopІгәНBottomІгЎЈХвСщөДөюІгЙијЖК№өГөзФҙІгәНөШІгҪфБЪЈ¬ҝЙТФұЈЦӨПөНіөзФҙөДНкХыРФЙијЖЈ»Н¬КұЈ¬ҙҰУЪРЕәЕІгЦ®јдөДөШІгҪ«4ёцРЕәЕІгУРР§өШёфАлҝӘЈ¬К№өГРЕәЕІгЦ®јдРЕәЕПЯјдөДҙ®ИЕҙпөҪЧоРЎЈ¬ТФұЈЦӨРЕәЕөД»ШБчВ·ҫ¶Ј¬ҙУ¶шұЈЦӨПөНіөДРЕәЕНкХыРФЎЈ

ЖдҙОЈ¬¶ФУЪПөНіЦРөДёЯЛЩЧЬПЯРЕәЕұШРлҪшРРЧиҝ№ЖҘЕдЈ¬ҙУ¶шјхЙЩРЕәЕ·ҙЙдј°РЕәЕөД№эіеЎЈіЈјыөДЖҘЕдНшВзУРҙ®РР¶ЛҪУј°ACІўРР¶ЛҪУЈ¬ҝјВЗөҪPCBІјПЯҝХјдөДУ°ПмЈ¬ЧЬПЯРЕәЕТ»°гІЙУГөзЧиҙ®РР¶ЛҪУөД·ҪКҪЈ¬¶шДЈДвКУЖөРЕәЕПЯФтІЙУГACІўРР¶ЛҪУөД·ҪКҪЎЈФЪПөНіЙијЖҪЧ¶ОЈ¬ҝЙТФ»щУЪIBISДЈРНАыУГHyperLynx·ВХжИнјюҪшРРІјПЯЗ°·ВХжЈ¬И·¶ЁЧиҝ№ЖҘЕдНшВ·ј°ІјПЯҝн¶ИЎЈЧЬПЯПөНіІЙУГ33 ΩөДҙ®РР¶ЛҪУЈ¬¶шДЈДвКУЖөРЕәЕПЯІЙУГ75 ΩөДACІўРР¶ЛҪУНшВзЎЈ

Чоә󣬶ФПөНіөДөзФҙЖҪГжәНөШҪшРР·ЦёоЈ¬ІўУРР§өШЕФВ·өШәНөзФҙЙПөД·ҙөҜФлЙщЈ¬ФЪәПККөДөШ·ҪФцјУИҘсоөзИЭЎЈИҘсоөзИЭөД·ЦІјУҰёГҫЎБҝҝҝҪьИҘсоРҫЖ¬Ј¬Н¬КұҫЎБҝФЪГҝёцөзФҙТэҪЕЙПҫщФИ·ЦІјТ»ёцөзИЭЎЈ

УЙУЪПөНіКЗёЯЛЩРЕәЕҙҰАнПөНіЈ¬ТтҙЛФЪІјПЯЗ°ҝЙТФАыУГHyperLynxҪшРРІјПЯЗ°·ВХжЈ¬МШұрКЗ¶ФПөНіЦРөДҙжҙўДЈҝйј°НшВзІо·ЦДЈҝйҪшРР·ВХжЈ¬И·¶ЁЧиҝ№ЖҘЕдНшВ·ј°ІјПЯҝн¶ИЎЈФЪІјПЯНкіЙЦ®әу»№ҝЙТФҪшРРІјПЯәу·ВХжЈ¬И·ұЈПөНіөДРЕәЕНкХыРФј°јхРЎПөНіөДөзҙЕ·шЙдёЙИЕЎЈ

ҪбУп

ұҫПөНіАыУГTI№«ЛҫөДЧЁУГКУЖөҙҰАнРҫЖ¬TMS320DM642НкіЙЛ«DSP¶аВ·КУЖөјаҝШПөНіЙијЖЎЈУлҙ«НіөД¶аВ·КУЖөјаҝШПөНіПаұИЈ¬ІЙУГЛ«DSPөД¶аВ·КУЖөјаҝШПөНіЙијЖјтөҘЈ¬ҝӘ·ўіЙұҫөНЈ¬ҝЙ№г·әУҰУГУЪГәМҝЎўёЦМъөИ№ӨТөПЦіЎјаҝШөДБмУтЎЈ

ұаХЯЧўЈәұҫОДОӘЖЪҝҜЛхВФ°жЈ¬И«ОДјыұҫҝҜНшХҫwww.mesnet.com.cnЎЈ

ІОҝјОДПЧ

[1] Texas Instruments Inc. TMS320DM642 Video/Imaging FixedPoint Digital Signal Processor Data ManualЈ¬2004.

[2] Texas Instruments Inc. TMS320C6000 DSP External Memory InterfaceЈЁEMIFЈ© Reference GuideЈ¬2004.

[3] Texas Instruments Inc. TMS320C64x DSP Video Port/VCXO Interpolate ControlЈЁVICЈ© Port Reference GuideЈ¬2007.

[4] Philips.SAA7113H, 9bit video input processorЈ¬199906.

[5] Xu Xiaoshen, Jiang Hongxu, Jin Liang. A MultiDSP System for HighӘІPerformance Video Applications[R].Communication Systems,2008. 11th IEEE Singapore International Conference on ICCS,2008Јә778782.

[6] ЦЬЕаұуЈ¬ГзіӨФЖЈ¬ОдЦҫёХ.Т»ЦЦ»щУЪТФМ«НшөДКУЖөјаҝШПөНіөДЙијЖ[J].ОўјЖЛг»ъРЕПўЈ¬2009Ј¬25 ЈЁ52Ј©Јә142144.

[7] Ту¶«ЖҪ.»щУЪDM642өД¶аКУЖө¶аҙ°ҝЪПөНіЙијЖ[D].Оч°ІЈәОч°ІөзЧУҝЖјјҙуС§Ј¬2009.

[8] ·ҪҝЛ·ю.»щУЪЛ«DSPөД¶аКУЖөәПіЙПФКҫПөНіЙијЖ[D].Оч°ІЈәОч°ІөзЧУҝЖјјҙуС§Ј¬2009.

Бх№уұҰЈЁЦъАн№ӨіМКҰЈ©Ј¬ЦчТӘСРҫҝ·ҪПтОӘ№ӨТөҝШЦЖПөНіЎўјјКхУлЙиұёЎЈ